摘要:设计了一种给单片毫米波集成电路(MMIC)中射频低噪声放大器(LNA)供电的电源模块。该电源模块集成在MMIC中并利用低压差线性稳压器(LDO)提供稳定的低噪声电源电压。由于传统LDO结构噪声较大,因此设计了一种电压预调节和RC低通滤波相结合的新型LDO结构来降低电路噪声,并针对RC低通滤波电路启动慢的缺点提出了一种快速启动的电路结构。利用SMIC 0.18 μm CMOS工艺对电路进行设计和仿真测试,测试结果表明,输入电源电压5 V,输出电压在1~4.2 V范围内可调,电压输出线性调整率(LNR)为8.2 mV/V,负载调整率(LDR)为83.3 μV/mA,输出噪声电压在1 kHz~100 kHz内的噪声积分为34.94 μVrms,满足LNA的供电要求。

0 引言

随着毫米波雷达技术在汽车自动驾驶方面的应用,汽车毫米波雷达渐渐向高集成、高精度、高可靠性方向发展。从目前的研究情况和产品报道来看,仅有少数几家公司能够提供MMIC车载雷达的解决方案,技术研发尚不能完全满足市场应用的需求。MMIC能够集成射频前端收发电路和中低频信号处理电路。其中射频LNA应用于毫米波信号接收端,它不仅要对接收到的微弱射频信号进行放大,而且在放大的过程中要尽可能少地引入噪声,以供后续电路对信号进行处理[1]。

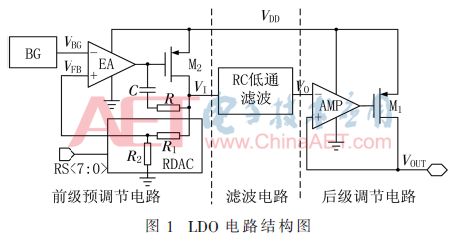

射频LNA由于对电源的噪声比较敏感,无法与其他模块共用一个电源管理单元(Power Management Unit, PMU),所以需要独立的电源模块。目前LDO低噪声优化设计主要分为两个方面0。第一方面如图1所示,通过改变传统LDO电路结构并添加RC滤波网络来降低电路噪声,这种结构能有效地滤除前级电路的高频噪声,但其缺点是需要外接片外电容,增加了一个芯片引脚。第二种方法不改变传统LDO的电路结构,由于噪声的主要来源是带隙基准源(BG)和误差放大器(EA),所以第二种方法通过设计低噪声的BG和EA来实现低噪声电压输出。这种方法无需片外电容,也不会增加芯片面积,但相对于第一种方法来说其降低高频噪声的效果较差。本文采用了新型的电路结构,同时也通过优化电路设计,尽量降低BG和EA的输出噪声。

1 LDO整体电路

图1所示为本文设计的LDO电路结构图,可以简单分为前级预调节电路、滤波电路、后级调节电路3个部分[3]。

其中M2为预调整管,通过RDAC模块中的R1、R2将电压VI输出为反馈电压VFB,并与带隙基准电压VBG经误差放大器EA相比较,通过控制M2的栅电压来达到控制电压VI的目的,由于噪声主要来源于BG、EA和R1、R2,所以电压VI通过低通滤波模块,滤除高频噪声,再通过放大器AMP和调整管M1产生低噪声输出VOUT[4]。其中RS<7:0>8位数字控制信号通过改变R1、R2的比例来控制输出电压VOUT。C1、R1组成相位补偿网络,通过调节电路主极点的位置,使反馈环路具有足够的相位裕度[5]。

通过式(5)可以看出通过电压预调节和RC低通滤波之后,整体输出噪声功率明显降低[8]。

2 各模块具体电路设计2.1 带隙基准源电路

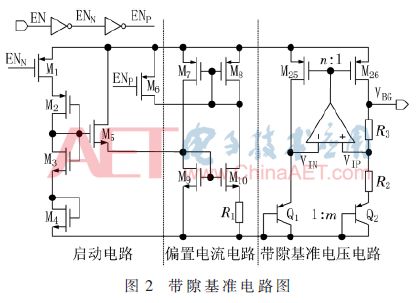

如图2所示,BG主要由3部分构成,分别是启动电路、偏置电流产生电路、VBG产生电路[9]。

其中EN为控制信号,当EN为1时,ENN为0,M1~M5导通,M5会向偏置电路注入电流,使其脱离简并点正常工作,而当EN为0时,电路停止工作。偏置电流产生电路通过电流镜和电阻的组合产生基准电流,这些基准电流为放大器提供基准电流输入。

BG的工作方式是通过正负温度系数的相互抵消,来实现电压基本不随温度变化的目的,VBG可表示为式(6)。

通过式(6)、式(7)可以得出,通过增大mn的乘积能够有效地减小噪声。

2.2 放大器电路

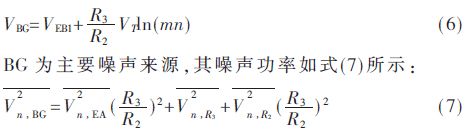

在BG、前级预调节环路和快速启动RC滤波电路中的放大器均采用折叠式共源共栅结构。它的好处是在保证足够的环路增益的情况下,电路具有较快的响应速度,电路引入的噪声适中,在可控范围内,具体电路如图3所示。

后级调整电路中的AMP采用经典二级运放结构。它的优点是高增益、低噪声并且具有比较大的输出电压摆幅[10]。

折叠式共源共栅结构的主要噪声来源为M7~M8、M9~M10、M15~M16。总的输入噪声分为热噪声和闪烁噪声两部分,其中输入热噪声为:

其中k为玻尔兹曼常数,T为绝度温度,gm为MOS管的跨导。输入闪烁噪声如式(9)所示。

2.3 快速启动低通滤波电路

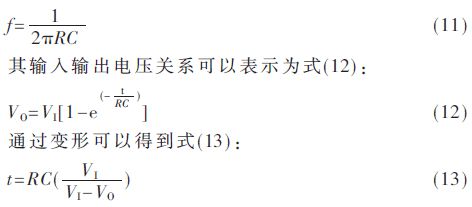

对于普通的RC滤波电路,其截止频率如式(11)所示:

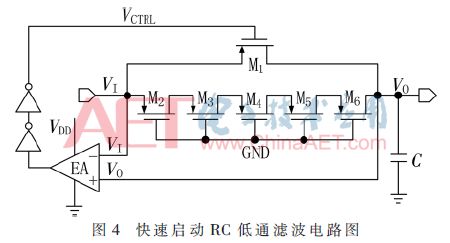

由式(10)可以看出滤除噪声的效果越好,RC低通滤波电路的启动时间就越长。针对这一缺点,提出了一种快速启动的RC低通滤波电路。如图4所示。

M1为开关管,M2~M6工作在深三极管区,可以看作是一系列的电阻串联。电路启动瞬间,VCTRL为低电平,M1导通,给电容C0充电,当VI=VO时,VCTRL转换为高电压,M1关断,此时,RC滤波电路开始工作。其中两个反相器级联对误差放大器(EA)输出电压进行数字化处理,使VCTRL更有效地控制开关M1。

本设计中电容C的取值在纳法量级,很难集成到芯片内部[11],所以采用芯片外部连接电容的方式,同时也会相应的增加一个芯片引脚。

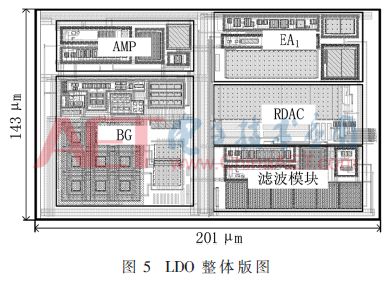

3 版图和整体电路仿真3.1 版图

图5所示为LDO的版图,整体芯片面积大约0.03 mm2。传统的LDO仅需要两个运放,本设计多使用了两个运放来满足低噪声和快速启动的实际需要,虽然相对来说增大了芯片的面积,但其性能上的优势足以弥补面积上的损耗。

3.2 整体电路仿真

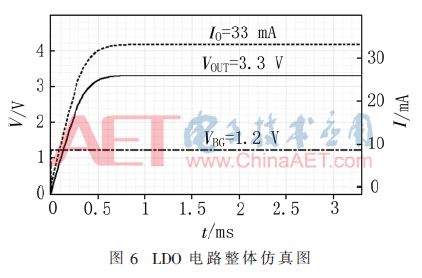

采用Cadence Spectre工具对整体电路仿真测试,图6所示为LDO整体电路测试结果。其中VDD=5 V,VOUT输出标准电源电压3.3 V。由图可以看出电路启动时间小于1 ms,整体电路有较好的稳定性。

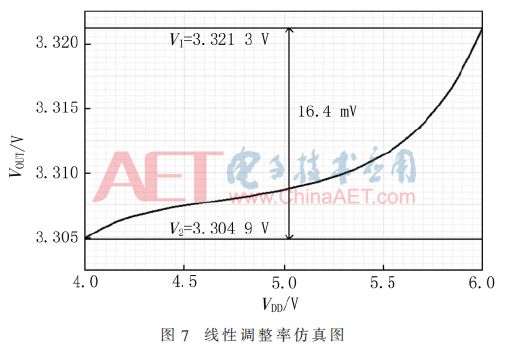

图7所示对电路的LNR进行仿真,VDD在4~6 V范围内变化,VOUT仅改变了16.4 mV。

通过计算可知其LNR为:

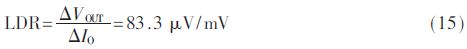

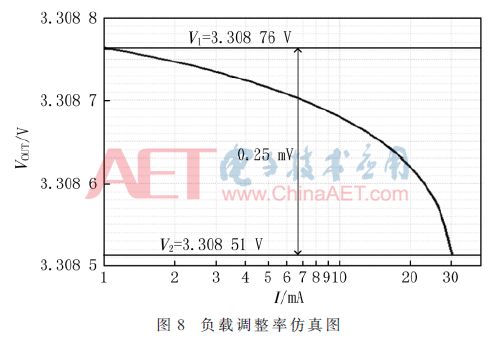

图8所示为电路LDR测试结果。其中负载电流在1~30 mA范围内变化,输出电压仅变化了0.25 mV。通过式(15)可以计算得出LDR为:

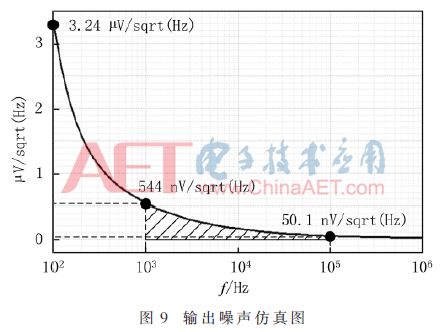

图9所示为输出噪声的仿真结果,图中所示的输出噪声密度(单位V/sqrt(Hz))曲线是对输出噪声功率(单位V2/Hz)进行开平方运算。

经计算,在1 kHz~100 kHz(阴影部分面积)范围内的噪声积分为34.94 μVrms。

4 结论

本文设计了一种给MMIC中LNA供电的电源模块,其性能参数对比如表1所示。从具体数据对比中可以看出本文设计的电源模块集成了电压基准源,并且具有较宽的输出电压范围和较小的输出噪声,各性能参数均满足设计应用的要求。

-

集成电路

+关注

关注

5396文章

11643浏览量

363704 -

射频

+关注

关注

104文章

5627浏览量

168325 -

ldo

+关注

关注

35文章

1955浏览量

154112

原文标题:【学术论文】射频LNA的低噪声LDO电源设计

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ALN3750-13-3335毫米波低噪声放大器WENTEQ

宽带低噪声放大器噪声分析

新型宽带低噪声放大器电路设计

CMD132低噪声放大器特征及阐述

Ka波段低噪声放大器的研镧

CMOS基毫米波低噪声放大器的研究

一种给单片毫米波集成电路中射频低噪声放大器供电的电源模块

一种给单片毫米波集成电路中射频低噪声放大器供电的电源模块

评论