-------- 探索FPGA 发展的不同时代

作者:Steve Trimberger,赛灵思公司,美国电子电气工程师协会 (IEEE) 研究员、美国计算机协会 (ACM) 院士、美国国家工程院院士

FPGA 器件自问世以来,已经经过了几个不同的发展阶段。驱动每个阶段发展的因素都是工艺技术和应用需求。正是这些驱动因素,导致器件的特性和工具发生了明显的变化。FPGA 经历了如下几个时代:

• 发明时代

• 扩展时代

• 积累时代

• 系统时代

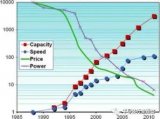

赛灵思于 1984 年发明了世界首款 FPGA,那个时候还不叫 FPGA,直到 1988 年 Actel 才让这个词流行起来。接下来的 30 年里,这种名为 FPGA 的器件,在容量上提升了一万多倍,速度提升了 一百倍,每单位功能的成本和能耗降低了一万多倍(见图 1)。

图 1:与 1988 年的赛灵思 FPGA 特征对比。价格和功耗降低一万倍。

这些进步主要由工艺技术所驱动, 而且人们很容易认为 FPGA 的发展只是随着工艺的发展简单地增大了容量。其实并没有这么简单。真正的故事要精彩得多。

发明时代:1984-1992 年

首款 FPGA,即赛灵思 XC2064,只包含 64 个逻辑模块,每个模块含有两个 3 输入查找表 (LUT) 和一个寄存器。按照现在的计算,该器件有 64 个逻辑单元——不足 1000 个逻辑门。尽管容量很小,XC2064 芯片的尺寸却非常大,比当时的微处理器还要大;而且采用 2.5 微米工艺技术勉强能制造出这种器件。

每功能的芯片尺寸和成本至关重要。XC2064 只有 64 个触发器,但由于芯片太大,成本高达数百美元。产量对大芯片来说是超线性的,因此芯片尺寸增加 5% 就会让成本翻一倍,让良率降至零,同时也导致初期的赛灵思无产品可卖。成本控制不仅仅是成本优化的问题;更是牵扯到公司生存问题。

在成本压力下,FPGA 架构师寻求通过架构和工艺创新来尽可能提高 FPGA 设计效率。尽管基于 SRAM 的 FPGA 是可重编程的,但是片上 SRAM 占据了 FPGA 大部分的芯片面积。基于反熔丝的 FPGA 以牺牲可重编程能力为代价,避免了 SRAM 存储系统片上占位面积过大问题。1990 年,最大容量的 FPGA 是基于反熔丝的 Actel 1280。Quicklogic 和 Crosspoint 也跟随 Actel 的脚步开发出基于反熔丝的 FPGA。为提高效率,架构经历了从复杂的 LUT 结构到 NAND 门再到单个晶体管的演变。

在发明时代,FPGA 是数量远远比用户的应用产品小得多。因此,多 FPGA 系统变得流行,自动化多芯片分区软件成为 FPGA 设计套件的重要组成部分。自动布局布线尚未有。完全不同的 FPGA 架构排除了通用设计工具的可能,因此 FPGA 厂商就担负起了为各自器件开发电子设计自动化 (EDA) 的任务。由于问题比较小,FPGA(逻辑和物理)手动设计是可以接受的。手动设计与优化通常很有必要,因为芯片上布线资源有限会带来很大设计挑战。

扩展时代:1992-1999 年

FPGA 初创公司都是无晶圆厂的公司,在当时属于新鲜事物。由于没有晶圆厂,他们在上世纪 90 年代初期通常无法获得领先的芯片技术。因此 FPGA 开启了扩展时代,此时落后于 IC 工艺的发展。到上世纪 90 年代后期,IC 代工厂意识到 FPGA 是理想的工艺发展推动因素,由此 FPGA 成为扫除工艺发展障碍的利器。代工厂只要能用新工艺产出晶体管和电线,就能制造基于 SRAM 的 FPGA。每一代新工艺的出现都会将晶体管数量增加一倍,使每功能成本减半,并将最大 FPGA 的尺寸增大一倍。化学-机械抛光(CMP)技术允许代工厂在 IC 上堆叠更多金属层,使 FPGA 厂商能够大幅增加片上互联,以适应更大的 LUT 容量(见图 2)。

图 2:FPGA LUT 和互连线路的增加。线路长度以数百万晶体管间距来测量。

占位面积变得不再像发明时代时那么宝贵。现在,占位面积可让位于性能、特性和易用性。更大的 FPGA 设计需要具有自动布局布线功能的综合工具。 到上世纪 90 年代末,自动综合、布局和布线已经成为设计流程的必要步骤。FPGA 公司的命运对 EDA 工具的依赖程度不亚于对 FPGA 功能的依赖程度。

最重要的是,实现容量翻番和片上 FPGA 逻辑成本减半的最简单方法是采用新一代工艺技术节点,因此,尽早采用新的工艺节点意义非凡。基于 SRAM 的 FPGA 在这个时期实现了明显的产品优势,因为它们率先采用了每种新工艺节点:基于 SRAM 的器件可立即使用密度更高的新工艺,而反熔丝在新节点上的验证工作则额外需要数月甚至数年时间。基于反熔丝的 FPGA 丧失了竞争优势。为获得上市速度和成本优势,架构创新与工艺改进相比就要退居其次。

积累时代:2000-2007 年

新千年伊始,FPGA 已成为数字系统中的通用组件。容量和设计尺寸快速增加,FPGA 在数据通信领域开辟了巨大市场。2000年代初期互联网泡沫破灭之后,迫切需要降低成本,这也减少了很多“临时”ASIC 用户。定制芯片对小的研发团队来说风险太大。当他们发现FPGA可以解决他们的问题,自然他们就变成了 FPGA 用户。

FPGA 问题不局限于典型问题,单纯提高容量不足以保证市场增长。FPGA 厂商通过如下两种方式解决了这一挑战。针对低端市场,厂商再度关注效率问题,并生产低容量、低性能、“低成本”的 FPGA 系列,例如赛灵思 Spartan® FPGA 系列。针对高端市场,FPGA 厂商通过开发针对重要功能的软逻辑 (IP) 库,努力让客户更方便地填充最大的 FPGA。这些软逻辑功能中最值得注意的是存储器控制器、各种通信协议模块(包括以太网 MAC),甚至软微处理器(如赛灵思 MicroBlaze™ 处理器)。

设计特点在 2000 年代发生了改变。大型 FPGA 容纳超大型设计(完整子系统)。FPGA 用户不再只是实现逻辑;他们需要使 FPGA 设计符合系统标准要求。这些标准主要是指信号和协议方面的通信标准,可用来连接外部组件或者实现内部模块通信。处理标准让 FPGA 在计算密集型应用中发挥越来越重要的作用。积累时代末期,FPGA 已不仅是门阵列,而且还是集成有可编程逻辑的复杂功能集。FPGA 俨然变成了一个系统。

系统时代:2008 年以后

为解决系统设计问题,FPGA 越来越多地整合系统模块:高速收发器、存储器、DSP 处理单元和完整处理器。同时还进一步集成了重要控制功能:比特流加密与验证、混合信号处理、电源与温度监控以及电源管理等。这些特性在 Zynq All-Programmable 器件中得到了充分体现。同时,器件也推动了工具的发展。系统 FPGA 需要高效的系统编程语言,现可利用 OpenCL 和 C 语言以类似软件的流程来编程。

FPGA 发展何时才能到头?可编程性的基本价值已经为业界所共识,小型、高效的逻辑操作可加速很多重要算法并降低功耗,FPGA 技术会持续存在, 并不断发展演进。

-

FPGA

+关注

关注

1629文章

21736浏览量

603235 -

触发器

+关注

关注

14文章

2000浏览量

61146

发布评论请先 登录

相关推荐

如何降低AD1247的功耗?

台积电2nm制成细节公布:性能提升15%,功耗降低35%

工业级SD卡:稳健发展,未来可期

FPGA发展阶段: 容量和速度提升_功耗和价格降低

FPGA发展阶段: 容量和速度提升_功耗和价格降低

评论