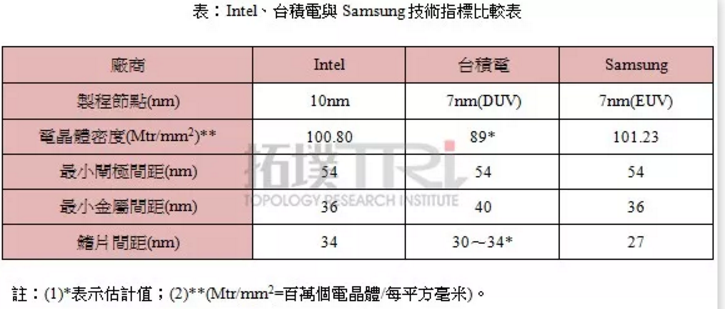

由于晶体管制造的复杂性,每代晶体管制程针对不同用途的制造技术版本,不同厂商的代次间统计算法也完全不同,单纯用代次来比较并不准确。根据目前业界常用晶体管密度来衡量制程水平,英特尔最新10nm制程的晶体管密度堪比三星 EUV版本7nm制程。

英特尔发挥IDM优势,优化电路设计达到比肩三星 7nm EUV微缩效果

根据技术指标(如下图所示)可以看出,三星 7nm采用EUV后,明显的贡献在三星 7nm EUV的鳍片间距仅为英特尔的80%左右,然而英特尔的解决方案则是借由设计端的优化。

例如减少Dummy Gate数量及Gate触点位置设计在晶体管上方(Contact on active gate,COAG)等,不仅获得良好的微缩效果更可减少制造端在制程上的负担,使得英特尔 10nm闸极间距及金属间距比肩三星 7nm EUV,并成功将10nm制程的晶体管密度提升至100.8 Mtr/mm2与三星 7nm EUV的101.23 Mtr/mm2同等水平,显示三星的7nm EUV与英特尔的10nm技术水平相当。

面临英特尔及三星的竞争,台积电仍有其优势

英特尔展示第三代10nm技术,向市场展现EUV并非制程微缩至10nm的必要条件,因此单就设计开发能力英特尔仍维持领先水平,台积电则因多年来服务代工客户的经验累积出完善的设计规范(design rule)有助于客户快速客制化芯片,最重要的是其稳定的良率表现深受客户信赖。

三星则倾向挑战领先同业采用EUV,以此提升自身制程技术来吸引客户投单,然而从英特尔采用EUV的保守态度来看,EUV很可能仍有其不稳定因素存在(如缺乏商用光化图形光罩检测及EUV光罩护膜准备不及等),三星能否驾驭EUV仍是一下挑战,在此状况下,客户倾向采用能快速客制化良率稳定的台积电机会最高。

-

英特尔

+关注

关注

61文章

10321浏览量

181073 -

三星电子

+关注

关注

34文章

15896浏览量

183222 -

台积电

+关注

关注

44文章

5810浏览量

177037 -

晶体管

+关注

关注

78文章

10439浏览量

148587

发布评论请先 登录

基于偏置电阻晶体管(BRT)的数字晶体管系列MUN2231等产品解析

MUN5136数字晶体管技术解析与应用指南

电压选择晶体管应用电路第二期

广汽集团三家科技企业同日挂牌上市

晶体管的定义,晶体管测量参数和参数测量仪器

英飞凌功率晶体管的短路耐受性测试

0.45-6.0 GHz 低噪声晶体管 skyworksinc

多值电场型电压选择晶体管结构

晶体管架构的演变过程

晶体管光耦的工作原理

下一代高速芯片晶体管解制造问题解决了!

2SC5200音频配对功率管PNP型晶体管

无结场效应晶体管详解

三家独大!在晶体管产业谁更厉害?

三家独大!在晶体管产业谁更厉害?

评论