大家好,又到了每日学习的时间了,今天我们来聊一聊英特尔 Altera系列 cyclone V HPS GIC.

一、CYCLONE V GIC配置

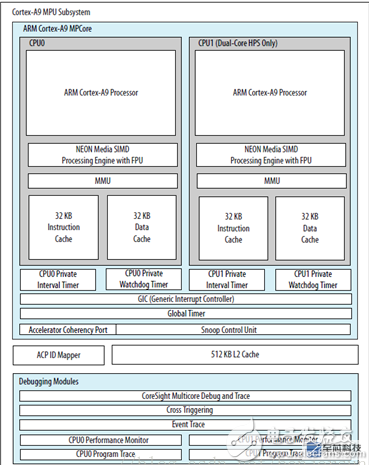

Cyclone v使用双核ARM CORTEX A9硬核处理器,MPU系统框图如下:

由上面图可以看出,双核CORTEXA9共同使用一个GIC,pl390。PL390实现了180个中断源,包括了专用的FPGA中断。每个核都有16个一组的软件中断(SGI)及16个一组的私有中断(PPI)。这32个中断占用了GIC的0-31中断号,也称为interrupt ID。但是这32个中断采用了中断与寄存器分区抽像。关于这个中断与寄存器分区,后面讲讲。具体的中断映射,请参照cyclone v HPS手册。

PL390负责收集所有的中断信号,并对这些中断信号进行管理,包括中断行为,中断路由及安全扩展等。具体如下:

l ARM安全扩展,这部分内容需要了解ARM TRUSTZONE技术。

l 使能,关闭及生成外围中断。

l 生成软件中断。

l 中断门限及优先级设置。

l 多处理器环境中的路由。

PL330支持三种中断类型,PPI,SPI,SGI。

l PPI中断为CPU核私有中断,只连接到指定CPU核。

l SPI由PL330路由到相应的CPU核。

l SGI由软件编程PL330直接生成,用与核间通信。

PL390支持两中中断模型:

l 1:N:只让一个CPU核处理中断。软件通过系统编程GIC实现中断路由,让指定CPU核处理该中断。

l N:N:每个处理器都会收到中断,它们独立处理这些中断。这种方式在SGI上使用,用于CPU核间通信。

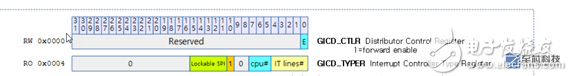

二、MPU GIC

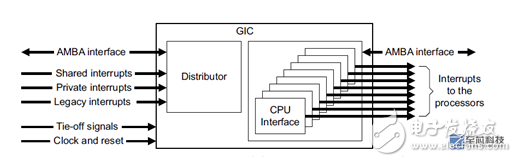

PL390提供一个AMBA总线接口给SOC系统访问其内部寄存器,可以进行可寻址配置及访问,同时还可以提供最多8个CPU接口,也就是说可以最多为8个CPU提供中断服务。

整个GIC被分成两个部分,distributor(中断分配器)与多个CPU接口。再看下面一张图。

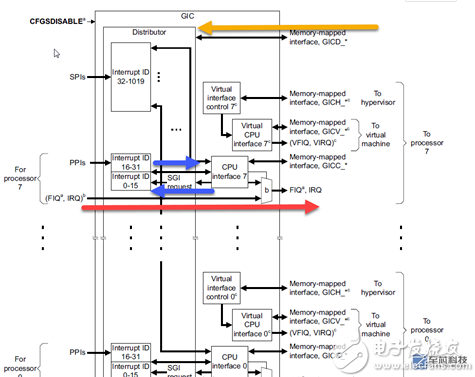

这张图中,红色箭头直接穿过distributor,分配到FIQ与IRQ,这就是bypass模式,也称为旁路模式,这种模式下,所有中断被直接分配到了相应的CPU核。而橙色箭头方向表示GIC提供了一个AXI接口,可以用于访问distributor,对GIC进行配置。蓝色表示软件可以通过CPU接口直接编程GIC,产生中断,该中断具有广播性质。

通用GIC系统框图如下所示:

由上图可以看到GIC明显分成了Distributor与cpu接口两部分。所有的中断都经过Distributor,SGI中断只是能edge触发。

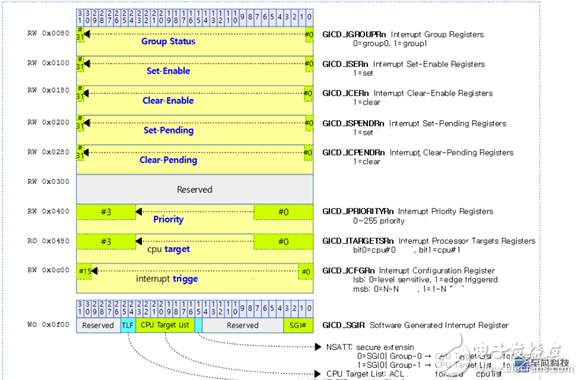

三、GIC编程模型

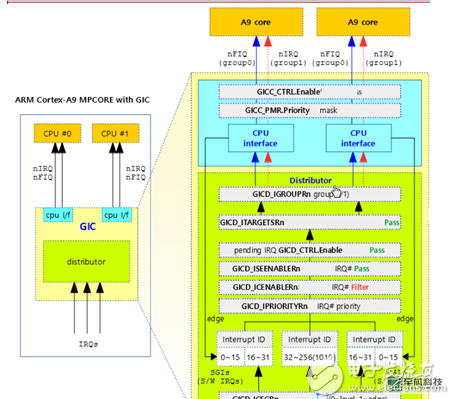

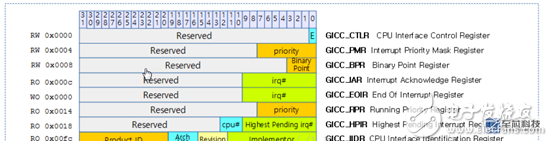

CPU接口寄存器如下图所示,在CYCLONE V中的偏移地址是0xfffec000。

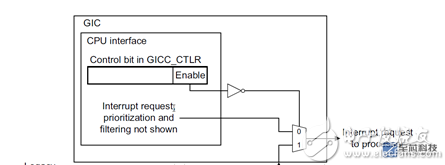

GICC_CTRL(CPU接口控制寄存器)

Enable= 1来转发中断。

中断优先级屏蔽寄存器(GICC_PMR)

用来设置一个优先级,低于该优先级的中断不会送到CPU。如果设置成0,那就意味着所有中断都屏蔽了,都不会送到ARM核。

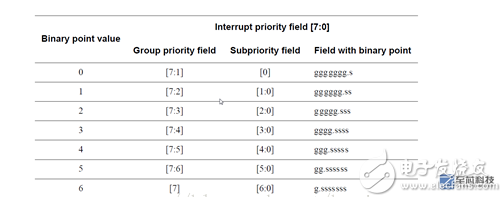

GICC_BPR(二进制点寄存器)

优先级值被分成组优先级与子优先级,跟IP地址掩码相似。这样设置后,有相同组优先级的中断被认为有相同的等级。这样就分成两种情况,如果一个中断要抢占一个正在活动的中断,那么该中断必须有一个比活动中断小的优先级。如果没有活动中断情况下,相同组的中断比较子优先级,产生一个。

GICC_IAR(中断确认寄存器)

当接收到中断时,读取该寄存器并读取中断ID及SGI中产生中断的CPUID,通知gic中断处理程序已被确认。

中断结束寄存器(GICC_EOIR)

当中断服务程序(ISR)中的中断处理完成时,记录相应的中断ID,并通知gic已执行eoi处理。写该寄存器通过GIC中断处理完毕。

-

英特尔

+关注

关注

60文章

9848浏览量

171197 -

Altera

+关注

关注

37文章

774浏览量

153792

发布评论请先 登录

相关推荐

测试芯片出炉 Altera/英特尔抢得14nm头筹

英特尔CEO亲自上阵解读重金收购Altera背后原因

为物联网带来惊喜 英特尔推出Cyclone10 FPGA系列

英特尔Altera系列cyclone V HPS GIC

英特尔Altera系列cyclone V HPS GIC

评论