大家好,又到了每日学习的时间了,今天咱们来聊一聊SDR、DDR、QDR存储器。

首先先简单的了解一下,然后在做一下比较。

SDR:Single Data Rate, 单倍速率

DDR:Dual Data Rate, 双倍速率

QDR:Quad Data Rate, 四倍速率

DRAM:Dynamic RAM, 动态随机存储器, 每隔一段时间就要刷新一次数据才能够保存数据

SRAM:Static RAM, 静态随机存储器, 静态随机存储器,不需要刷新电路,数据不会丢失

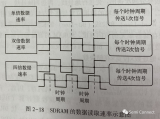

SDRAM: Synchronous DRAM, 同步状态随机存储器,数据的读写需要时钟来同步

下面来做个比较:

1、 SRAM和DRAM、SDRAM而言,都有DDR和QDR的一说。QDR,DDR只是说速率,和DRAM/SRAM的区分无关。而且由于实现工艺的原因,DRAM和SDRAM容量比SRAM大,但是读写速度不如SRAM。此外它们一般都是应用于RAM类型的存储器的速率。

2 、SDR只在时钟的上升沿传输数据,读写是在同一条数据总线进行,读写不能同时进行,而DDR 是在SDR的基础上改进,它可以在时钟的上升,下升沿时同时传递一次数据,也就是相当于SDR的两倍,但读写还是不能同步进行,而QDR,集读写上下传输于一身,成为具有一进,一出相当于两个DDR的数据接口,四个SDR 所能达到的效果。

3、SRAM其实是一种非常重要的存储器,它的用途广泛。SRAM的速度非常快,在快速读取和刷新时能够保持数据完整性。SRAM内部采用的是双稳态电路的形式来存储数据。所以SRAM的电路结构非常复杂。制造相同容量的SRAM比DRAM的成本高的多。正因为如此,才使其发展受到了限制。因此目前SRAM基本上只用于CPU内部的一级缓存(cache)以及内置的二级缓存,仅有少量的网络服务器以及路由器上能够使用SRAM。

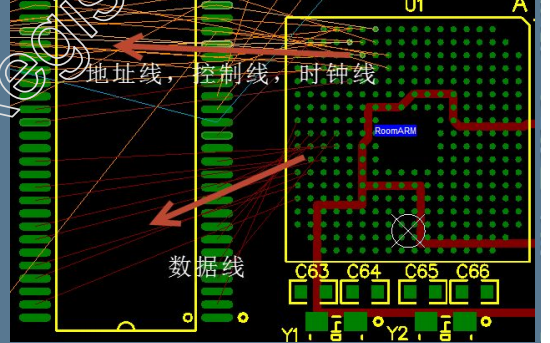

4、一般嵌入式产品里面的内存都是用的SDRAM,电脑的内存用的也是SDRAM,叫DDR SDRAM,其集成度非常高,因为是动态的,所以必须有刷新电路,每隔一段时间必须得刷新数据。

今天就聊到这里,各位,加油。

-

存储器

+关注

关注

38文章

7553浏览量

164906 -

SDR

+关注

关注

7文章

234浏览量

50680

发布评论请先 登录

相关推荐

简单认识双倍速率同步动态随机存取存储器

详解:SDR/DDR/DDR2/SDRAM的功能及异同

SRAM存储器如何在网络设计系统的应用

Cyclone IV 器件中的外部存储器接口

哪种类型的同步SRAM用于外部存储器?

业界最快QDR SRAM(静态随机存取存储器)

PCB的常用存储器设计的详细资料说明

LTC3776演示电路-2相,550 KHz,用于DDR/QDR存储器的同步转换器(3.3V至2.5V@3A和1.25V@3A)

LTC3776:用于DDR/QDR存储器终端的双2相无RSENSE同步控制器产品手册

LTC3717-1:宽工作范围,无RSENSE降压控制器,用于DDR/QDR存储器终端数据表

LTC3718:适用于DDR/QDR存储器终端的低输入电压DC/DC控制器产品手册

LTC3717:宽工作范围,无RSENSE降压控制器,用于DDR/QDR存储器终端数据表

简谈SDR、DDR、QDR存储器的比较

简谈SDR、DDR、QDR存储器的比较

评论