上一篇说到了软件的安装以及破解,还有附带的网盘里的软件安装包都分享给大家了。这一篇咱们就来说一说FPGA工程的建立。

点击桌面的quartus 的图标,打开软件。

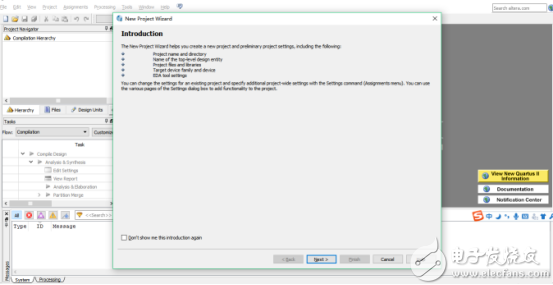

然后点击软件上面的菜单:点击FIFE --New projiec,建立一个新的工程。

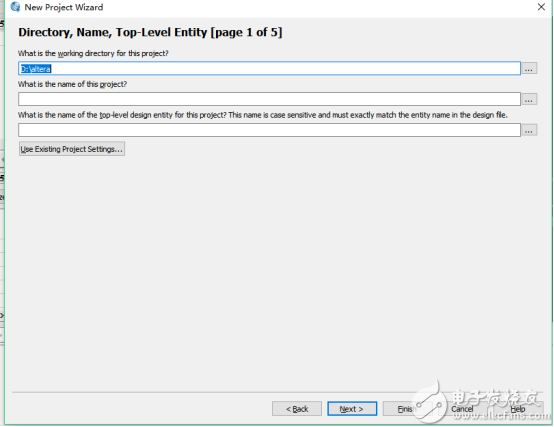

点击下一步,会出现如下的窗口,问你你的工作路径,和工程的名字,还有顶层的名字(注意:工程一定不要放在C盘,还有文件名为中文,这样会编译不过去,也可认为是错误的操作)。给你的工程起个名字后然后下一步。

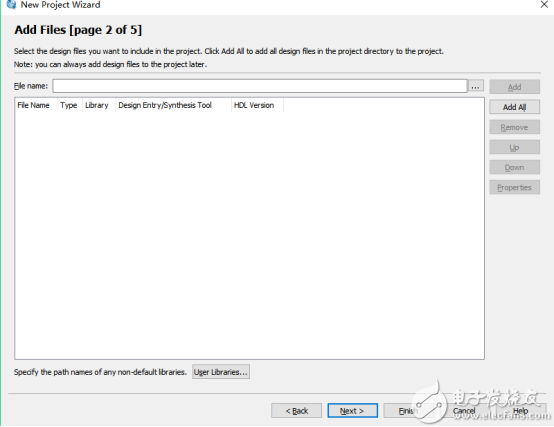

继续下一步(这个页面表示你可以添加文件,在我们quartus 中文件都是 .v文件)

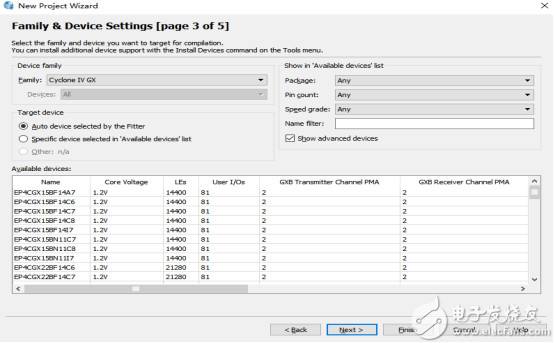

下一步后出现如下的页面,这个页面是选择我们用的开发板的芯片型号,一般芯片的型号都在板子中FPGA芯片的正上方写的,大家可以认真的观看后选择,如果选择错误的芯片信息,会导致我们给端口分配引脚的时候分配不上去,下板当然也下载不进去。

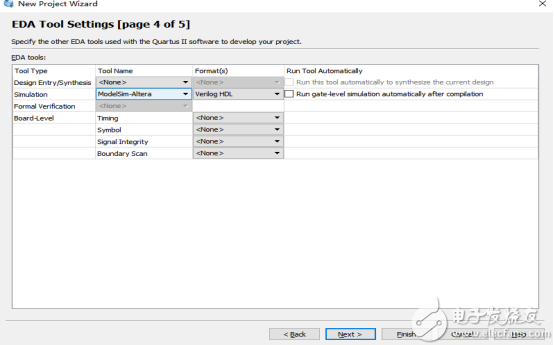

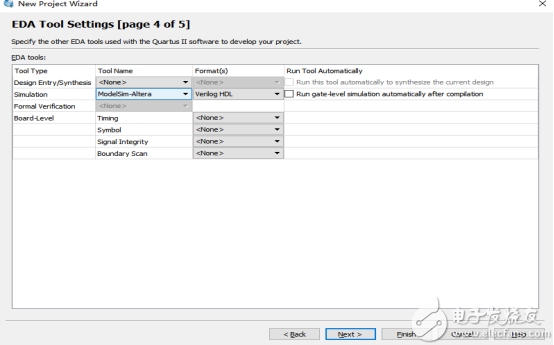

选择正确的芯片后下一步,这个页面是我们可以选择simulation(仿真)的信息,我们通过下拉选择我们的仿真工具,还有语言,楼主用的是verilog,如下图选择。

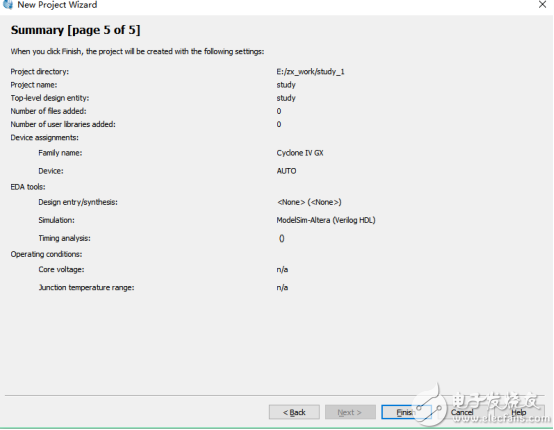

点击下一步后会出现一个页面,这个页面是告诉我们工程的信息,比如工程名,工程路径,芯片等,建议一次选择正确(我们也可以在简历工程后来修改这些)

然后点击Finish,这样就成功的创建了工程。

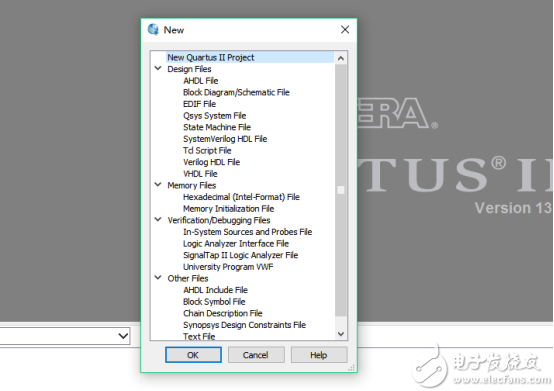

我们建好工程后,就需要写代码等,点击Fife,选择New----VHDL File。

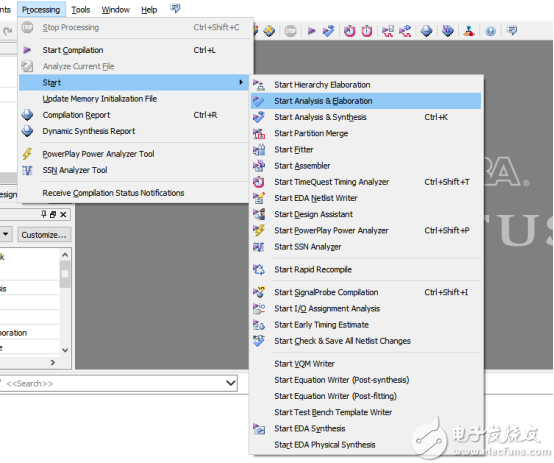

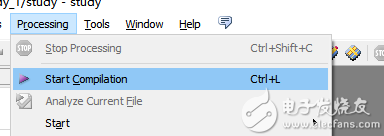

然后当我们写好代码后,按如下图的操作,编译通过以后,进行下一步,反之查看错误的地方,找出错误并改正。

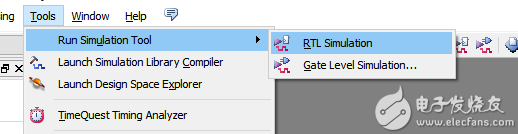

编译通过后,我们可以写我们软件的激励,也叫测试,然后仿真我们的代码是否正确,如下图的操作。

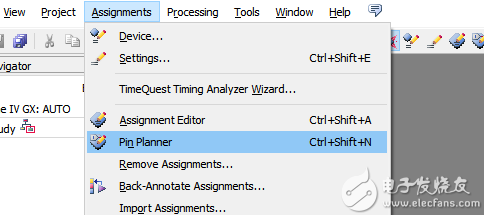

如果仿真也没有问题了,我们就可以给我们代码的端口分配关键,如下图。

然后全编译,生成下载文件。

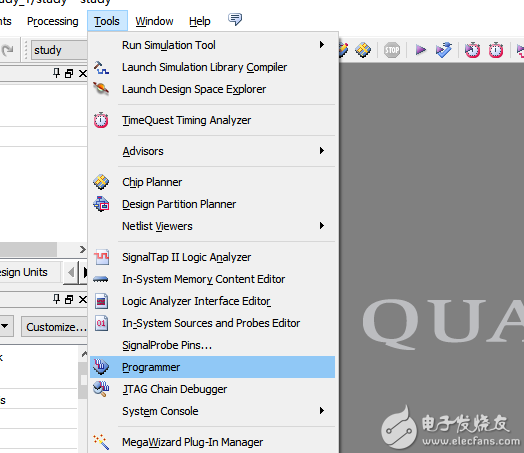

等编译通过后,下载,如下图。

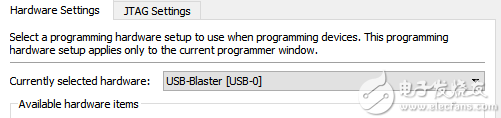

连接我们FPGA板子和下载线,安装好驱动,然后选择如下:

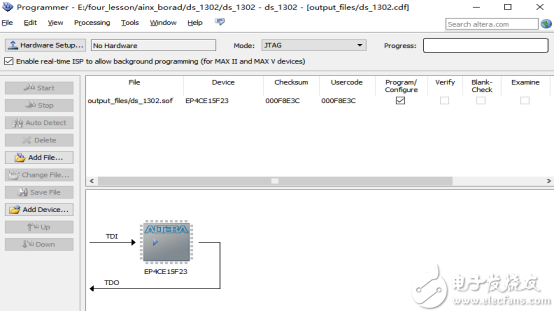

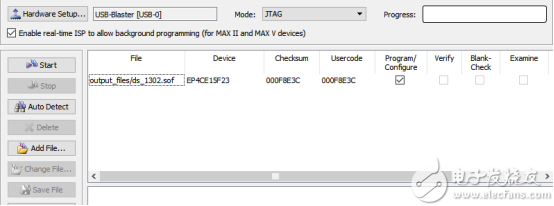

之后会出现下面的界面:

然后点击开始,如果没有.sof文件,大家可以点击

然后从文件夹中添加sof文件,操作截图如下:

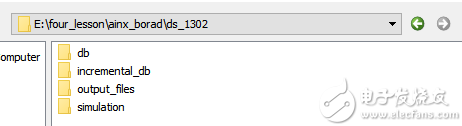

然后出现你的工程目录,点击output_files文件,打开就有.sof文件,选择就好了。

通过以上步骤,大家基本都掌握了软件的一些简单的操作,在以后更新的文章中会分享一些小项目等,希望大家多多关注。

如果有什么问题,可以加FPGA交流群:282124839,欢迎大家共同交流学习。

-

FPGA

+关注

关注

1630文章

21766浏览量

604565 -

quartus

+关注

关注

16文章

171浏览量

74666

发布评论请先 登录

相关推荐

FPGA学习手记 FPGA入门及建立FPGA开发环境

Xilinx FPGA入门连载7:新建工程

FPGA学习整理

【NUCLEO-F412ZG试用体验】用标准库建立STM32F412ZG工程与模板分享

如何学习设计FPGA?

FPGA零基础学习:Intel FPGA 开发流程(上)

STM32建立文件夹

建立一个关于stm32的工程

FPGA基础教程系列—Quartus工程建立

FPGA学习系列:2. 工程project的建立

FPGA学习系列:2. 工程project的建立

评论