PGA基本特点

1) 采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。

2) FPGA可做其它全定制或半定制ASIC电路的中试样片。

3) FPGA内部有丰富的触发器和I/O引脚。

4) FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

5) FPGA采用高速CMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

FPGA三大优势

优势一:更大的并行度

这个主要是通过并发和流水两种技术实现。A:并发是指重复分配计算资源,使得多个模块之间可以同时独立进行计算。这一点与现在的多核和SIMD技术相似。但相对与SIMD技术,FPGA的并发可以在不同逻辑功能之间进行,而不局限于同时执行相同的功能。举个简单例子说就是使用SIMD可以同时执行多个加法,而FPGA可以同时执行多个加法和乘法和任何你能设计出来的逻辑。

B:流水是通过将任务分段,段与段之间同时执行。其实这一点和CPU相似,只是CPU是指令间的流水而FPGA是任务间流水或者可以说是线程间流水。

优势二:可定制

FPGA内部通过LookupTable实现逻辑,可以简单理解为是硬件电路。可定制指的是在资源允许范围内,用户可实现自己的逻辑电路。通常情况下任务在硬件电路上跑是比在软件上快的,比如要比较一个64位数高32位和低32位的大小,在CPU下需要2条区数指令,两条位与指令,一条移位指令一条比较指令和一条写回指令,而在FPGA下只要一个比较器就行了。

优势三:可重构

可重构指的是FPGA内部的逻辑可根据需求改变,减少开发成本。同时,使用FPGA复用资源比使用多个固定的ASIC模块为服务器省下更多的空间。

FPGA工作原理

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括 可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。 现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

FPGA典型应用领域

一、数据采集和接口逻辑领域

1.FPGA在数据采集领域的应用

由于自然界的信号大部分是模拟信号,因此一般的信号处理系统中都要包括数据的采集功能。通常的实现方法是利用A/D转换器将模拟信号转换为数字信号后,送给处理器,比如利用单片机(MCU)或者数字信号处理器(DSP)进行运算和处理。

对于低速的A/D和D/A转换器,可以采用标准的SPI接口来与MCU或者DSP通信。但是,高速的A/D和D/A转换芯片,比如视频Decoder或者Encoder,不能与通用的MCU或者DSP直接接口。在这种场合下,FPGA可以完成数据采集的粘合逻辑功能。

2.FPGA在逻辑接口领域的应用

在实际的产品设计中,很多情况下需要与PC机进行数据通信。比如,将采集到的数据送给PC机处理,或者将处理后的结果传给PC机进行显示等。PC机与外部系统通信的接口比较丰富,如ISA、PCI、PCIExpress、PS/2、USB等。

传统的设计中往往需要专用的接口芯片,比如PCI接口芯片。如果需要的接口比较多,就需要较多的外围芯片,体积、功耗都比较大。采用FPGA的方案后,接口逻辑都可以在FPGA内部来实现了,大大简化了外围电路的设计。

在现代电子产品设计中,存储器得到了广泛的应用,例如SDRAM、SRAM、Flash等。这些存储器都有各自的特点和用途,合理地选择储存器类型可以实现产品的最佳性价比。由于FPGA的功能可以完全自己设计,因此可以实现各种存储接口的控制器。

3.FPGA在电平接口领域的应用

除了TTL、COMS接口电平之外,LVDS、HSTL、GTL/GTL+、SSTL等新的电平标准逐渐被很多电子产品采用。比如,液晶屏驱动接口一般都是LVDS接口,数字I/O一般是LVTTL电平,DDRSDRAM电平一般是HSTL的。

在这样的混合电平环境里面,如果用传统的电平转换器件实现接口会导致电路复杂性提高。利用FPGA支持多电平共存的特性,可以大大简化设计方案,降低设计风险。

二、高性能数字信号处理领域

无线通信、软件无线电、高清影像编辑和处理等领域,对信号处理所需要的计算量提出了极高的要求。传统的解决方案一般是采用多片DSP并联构成多处理器系统来满足需求。

但是多处理器系统带来的主要问题是设计复杂度和系统功耗都大幅度提升,系统稳定性受到影响。FPGA支持并行计算,而且密度和性能都在不断提高,已经可以在很多领域替代传统的多DSP解决方案。

例如,实现高清视频编码算法H.264。采用TI公司1GHz主频的DSP芯片需要4颗芯片,而采用Altera的StratixIIEP2S130芯片只需要一颗就可以完成相同的任务。FPGA的实现流程和ASIC芯片的前端设计相似,有利于导入芯片的后端设计。

三、其他应用领域

除了上面一些应用领域外,FPGA在其他领域同样具有广泛的应用。

(1)汽车电子领域,如网关控制器/车用PC机、远程信息处理系统。

(2)军事领域,如安全通信、雷达和声纳、电子战。

(3)测试和测量领域,如通信测试和监测、半导体自动测试设备、通用仪表。

(4)消费产品领域,如显示器|、投影仪、数字电视和机顶盒、家庭网络。

(5)医疗领域,如软件无线电、电疗|、生命科学。

数据中心为什么使用FPGA?

众所周知,通用处理器(CPU)的摩尔定律已入暮年,而机器学习和Web服务的规模却在指数级增长。人们使用定制硬件来加速常见的计算任务,然而日新月异的行业又要求这些定制的硬件可被重新编程来执行新类型的计算任务。

FPGA(FieldProgrammableGateArray)正是一种硬件可重构的体系结构,常年来被用作专用芯片(ASIC)的小批量替代品,然而近年来在微软、百度等公司的数据中心大规模部署,以同时提供强大的计算能力和足够的灵活性。

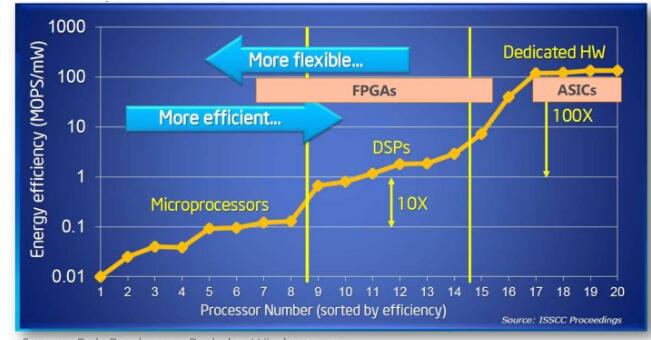

FPGA为什么快?「都是同行衬托得好」。CPU、GPU都属于冯·诺依曼结构,指令译码执行、共享内存。FPGA之所以比CPU甚至GPU能效高,本质上是无指令、无需共享内存的体系结构带来的福利。

冯氏结构中,由于执行单元(如CPU核)可能执行任意指令,就需要有指令存储器、译码器、各种指令的运算器、分支跳转处理逻辑。由于指令流的控制逻辑复杂,不可能有太多条独立的指令流,因此GPU使用SIMD(单指令流多数据流)来让多个执行单元以同样的步调处理不同的数据,CPU也支持SIMD指令。而FPGA每个逻辑单元的功能在重编程(烧写)时就已经确定,不需要指令。

冯氏结构中使用内存有两种作用。一是保存状态,二是在执行单元间通信。由于内存是共享的,就需要做访问仲裁;为了利用访问局部性,每个执行单元有一个私有的缓存,这就要维持执行部件间缓存的一致性。对于保存状态的需求,FPGA中的寄存器和片上内存(BRAM)是属于各自的控制逻辑的,无需不必要的仲裁和缓存。对于通信的需求,FPGA每个逻辑单元与周围逻辑单元的连接在重编程(烧写)时就已经确定,并不需要通过共享内存来通信。

说了这么多三千英尺高度的话,FPGA实际的表现如何呢?我们分别来看计算密集型任务和通信密集型任务。

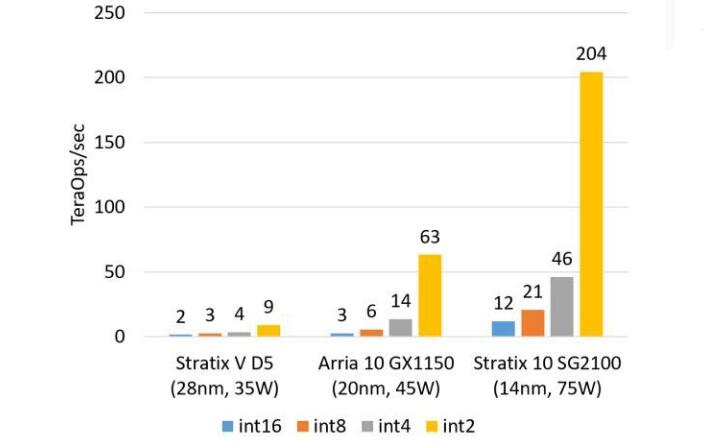

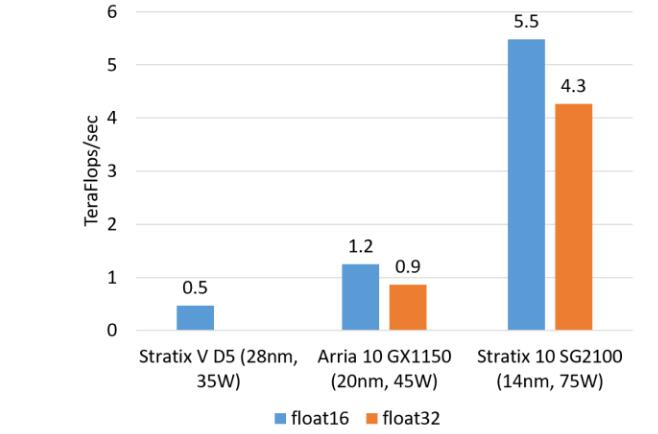

计算密集型任务的例子包括矩阵运算、图像处理、机器学习、压缩、非对称加密、Bing搜索的排序等。这类任务一般是CPU把任务卸载(offload)给FPGA去执行。对这类任务,目前我们正在用的Altera(似乎应该叫Intel了,我还是习惯叫Altera……)StratixVFPGA的整数乘法运算性能与20核的CPU基本相当,浮点乘法运算性能与8核的CPU基本相当,而比GPU低一个数量级。我们即将用上的下一代FPGA,Stratix10,将配备更多的乘法器和硬件浮点运算部件,从而理论上可达到与现在的顶级GPU计算卡旗鼓相当的计算能力。

FPGA的整数乘法运算能力(估计值,不使用DSP,根据逻辑资源占用量估计)

FPGA的浮点乘法运算能力(估计值,float16用软核,float32用硬核)

在数据中心,FPGA相比GPU的核心优势在于延迟。像Bing搜索排序这样的任务,要尽可能快地返回搜索结果,就需要尽可能降低每一步的延迟。如果使用GPU来加速,要想充分利用GPU的计算能力,batchsize就不能太小,延迟将高达毫秒量级。使用FPGA来加速的话,只需要微秒级的PCIe延迟(我们现在的FPGA是作为一块PCIe加速卡)。未来Intel推出通过QPI连接的Xeon+FPGA之后,CPU和FPGA之间的延迟更可以降到100纳秒以下,跟访问主存没什么区别了。

FPGA为什么比GPU的延迟低这么多?这本质上是体系结构的区别。FPGA同时拥有流水线并行和数据并行,而GPU几乎只有数据并行(流水线深度受限)。例如处理一个数据包有10个步骤,FPGA可以搭建一个10级流水线,流水线的不同级在处理不同的数据包,每个数据包流经10级之后处理完成。每处理完成一个数据包,就能马上输出。而GPU的数据并行方法是做10个计算单元,每个计算单元也在处理不同的数据包,然而所有的计算单元必须按照统一的步调,做相同的事情(SIMD,SingleInstructionMultipleData)。这就要求10个数据包必须一起输入、一起输出,输入输出的延迟增加了。当任务是逐个而非成批到达的时候,流水线并行比数据并行可实现更低的延迟。因此对流式计算的任务,FPGA比GPU天生有延迟方面的优势。

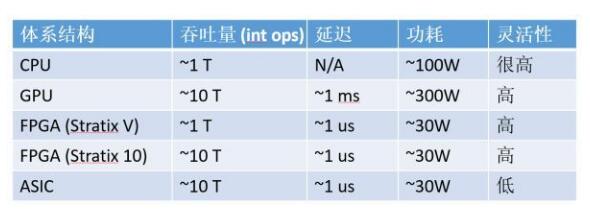

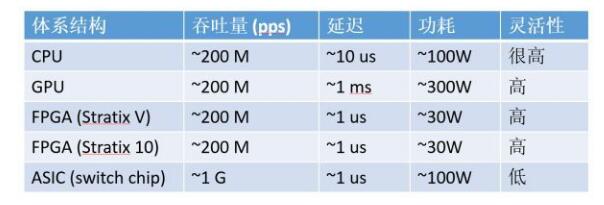

计算密集型任务,CPU、GPU、FPGA、ASIC的数量级比较(以16位整数乘法为例,数字仅为数量级的估计

ASIC专用芯片在吞吐量、延迟和功耗三方面都无可指摘,但微软并没有采用,出于两个原因:

数据中心的计算任务是灵活多变的,而ASIC研发成本高、周期长。好不容易大规模部署了一批某种神经网络的加速卡,结果另一种神经网络更火了,钱就白费了。FPGA只需要几百毫秒就可以更新逻辑功能。FPGA的灵活性可以保护投资,事实上,微软现在的FPGA玩法与最初的设想大不相同。

数据中心是租给不同的租户使用的,如果有的机器上有神经网络加速卡,有的机器上有Bing搜索加速卡,有的机器上有网络虚拟化加速卡,任务的调度和服务器的运维会很麻烦。使用FPGA可以保持数据中心的同构性。

接下来看通信密集型任务。相比计算密集型任务,通信密集型任务对每个输入数据的处理不甚复杂,基本上简单算算就输出了,这时通信往往会成为瓶颈。对称加密、防火墙、网络虚拟化都是通信密集型的例子。

通信密集型任务,CPU、GPU、FPGA、ASIC的数量级比较(以64字节网络数据包处理为例,数字仅为数量级的估计)

对通信密集型任务,FPGA相比CPU、GPU的优势就更大了。从吞吐量上讲,FPGA上的收发器可以直接接上40Gbps甚至100Gbps的网线,以线速处理任意大小的数据包;而CPU需要从网卡把数据包收上来才能处理,很多网卡是不能线速处理64字节的小数据包的。尽管可以通过插多块网卡来达到高性能,但CPU和主板支持的PCIe插槽数量往往有限,而且网卡、交换机本身也价格不菲。

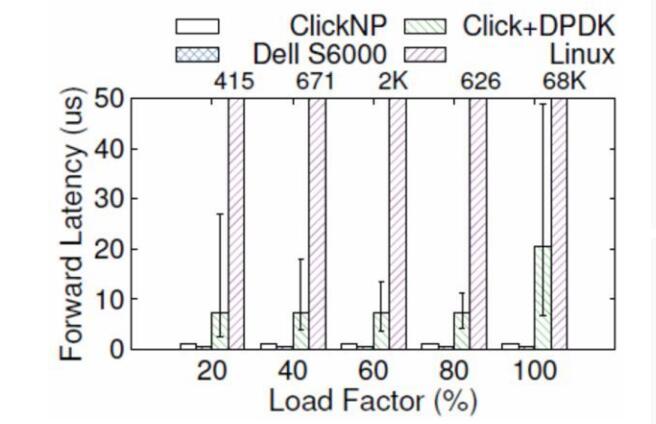

从延迟上讲,网卡把数据包收到CPU,CPU再发给网卡,即使使用DPDK这样高性能的数据包处理框架,延迟也有4~5微秒。更严重的问题是,通用CPU的延迟不够稳定。例如当负载较高时,转发延迟可能升到几十微秒甚至更高(如下图所示);现代操作系统中的时钟中断和任务调度也增加了延迟的不确定性。

虽然GPU也可以高性能处理数据包,但GPU是没有网口的,意味着需要首先把数据包由网卡收上来,再让GPU去做处理。这样吞吐量受到CPU和/或网卡的限制。GPU本身的延迟就更不必说了。

那么为什么不把这些网络功能做进网卡,或者使用可编程交换机呢?ASIC的灵活性仍然是硬伤。尽管目前有越来越强大的可编程交换机芯片,比如支持P4语言的Tofino,ASIC仍然不能做复杂的有状态处理,比如某种自定义的加密算法。

综上,在数据中心里FPGA的主要优势是稳定又极低的延迟,适用于流式的计算密集型任务和通信密集型任务。

-

FPGA

+关注

关注

1624文章

21597浏览量

601006 -

cpu

+关注

关注

68文章

10794浏览量

210659 -

数据中心

+关注

关注

16文章

4613浏览量

71866

发布评论请先 登录

相关推荐

tdms数据存储的时候,每运行一次,数据不断的往下接,行数会越来越多,怎么解决这个问题,让行数不变

生产者消费者队列状态数据越来越多如何解决?

防止越来越多的线束把车体挤爆,CAN-BUS技术应需而生

为什么变频串联谐振会被应用的越来越多?

消费电子产品需要越来越多的容量来存储数字内容

为什么用代还软件的人越来越多?代还软件找谁开发

如何应对数据中心管理的挑战

数据中心和光学互连的增长趋势

视频监控系统中越来越多的使用了高级的数据存储设备和系统

为何越来越多的企业使用AGV小车?

FPGA在电机控制中的使用越来越多

为什么越来越多的企业使用SaaS系统?

为什么数据中心使用FPGA越来越多?

为什么数据中心使用FPGA越来越多?

评论