设计背景:

Verilog语法中很多情况都用到了串并转化的思想,旨在与提升运算和芯片运行的速度,串行转并行已经成为设计中不可缺少的一种思维。

设计原理:

本次的设计主设计一个8位的串并转化,意思就是当输入8个数据的时候,我们把这8个串行数据转化为8位的并行数据然后输出出来。也就是需要一个8位的寄存器,来一个数据存到对应的位上,然后输出出来就完成了本次设计。

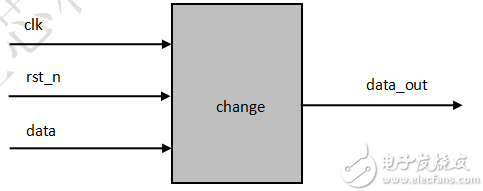

设计架构图:

设计代码:

设计模块

0modulestudy(clk,rst_n,data,data_out);//端口列表

1

2 inputclk,rst_n;//时钟,复位输入

3 inputdata;//输入数据

4

5 outputreg[7:0]data_out;

6

7 reg[3:0]count;

8 reg[7:0]temp;

9

10 always@(posedgeclk)//时序逻辑

11 if(!rst_n)

12 begin

13 data_out <=0;

14 temp <=0;

15 count <=0;

16 end

17 elseif(count <8)//计数表示只接8个数据

18 begin

19 temp <={temp[6:0],data};//移位寄存器

20 count <=count +1'b1;

21 end

22 else

23 begin

24 data_out <=temp;//接到后输出

25 end

26

27endmodule

测试模块

0`timescale1ns/1ps//时标

1

2moduletb();

3

4 regclk,rst_n;

5 regdata;

6

7 wire[7:0]data_out;

8

9 study study_dut(//设计例化

10 .clk(clk),

11 .rst_n(rst_n),

12 .data(data),

13 .data_out(data_out)

14 );

15

16 initialbegin

17 clk =1;

18 rst_n =0;//复位

19 data =0;

20 #200rst_n =1;//不复位

21 data =1;//模拟数据输入

22 #20data =0;

23 #20data =1;

24 #20data =0;

25

26 #20data =0;

27 #20data =1;

28 #20data =0;

29 #20data =1;

30

31 #200$stop;

32 end

33

34 always#10clk =~clk;//模拟晶振时钟

35

36endmodule

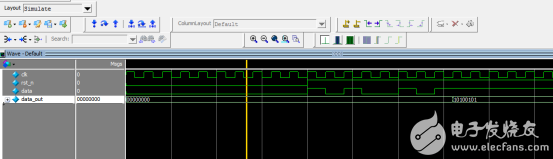

仿真图:

在测试中模拟数据输入时1010 0101,然后输出是一个并行数据,那么通过看仿真时序,清楚的看到输出是8位的并行数据,本次设计正确.

同样大家可以自己推理设计出并转串的逻辑电路来。

-

FPGA

+关注

关注

1631文章

21807浏览量

606726 -

串并转换

+关注

关注

0文章

3浏览量

7857

发布评论请先 登录

相关推荐

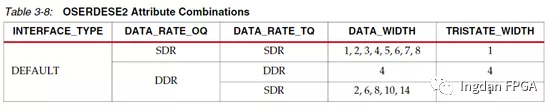

如何使用其gearbox功能来实现不同的比率的串并转换功能

LVDS串并转换与并串转换设计

FPGA学习系列:7. 串并转换

FPGA学习系列:7. 串并转换

评论