设计背景:

状态机是描述各种复杂时序的时序行为,是使用HDL进行数学逻辑设计中非常重要的方法之一,状态机分为摩尔机和米粒机,当输出只和状态有关系的话称为摩尔机,当输出不仅和状态有关系也和输入信号有关系的时候称为米粒机,米粒机和摩尔机的电路原型我就不在这里给大家介绍了。

状态机是由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设计的状态进行状态的转移,是协调相关信号的动作,完成特定操作的控制中心。比如我们生活中遇到的问题,健康---感冒---健康,这个就是一个状态的转移图,从健康状态到感冒状态在到健康状态。

设计原理:

我认为对于我们初学者来说我们只要只要状态机就是当这个状态也就是当这个时钟来的时候发生这件事情,当下各时钟来的时候发生另一件事,也就是说发生这件事后,跳转下一个时钟发生另一件事情,两个事情发生没有关系。我们理解初学者理解这个就行了,不用理解高深的二段式,三段式。

我们会在下面的设计中用到简单的状态机让大家明白简单的状态机。

我们的设计也是一个流水灯,我们的设计是在复位的时候让4个等全熄灭,第一个上升沿点亮一个,第二个点亮下一个,依次类推。

我们的写法可以这样想,当第一个状态也就是一个上升沿点亮第一个灯,然后跳转下一个状态点亮第二个灯,第三个点亮下一个。。。。

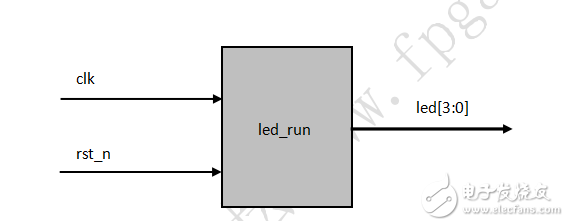

设计架构图:

设计代码:

设计模块

0moduleled_run (clk,rst_n,led);

1

2 inputclk,rst_n; //定义输入输出

3

4 outputreg[3:0]led;

5

6 reg[10:0]count; //定义一个时间寄存器

7 regclk_1hz; //定义一个时钟

8 reg[1:0]state;//定义状态

9

10 always@(posedgeclk)

11 if(!rst_n)

12 begin

13 clk_1hz <=1;

14 count <=0;

15 end

16 elseif(count <(5/1/2-1))//计数来产生一个时钟

17 count <=count +1'd1;

18 else

19 begin

20 count <=26'd0;

21 clk_1hz <=~clk_1hz;

22 end

23

24 always@(posedgeclk_1hz)

25 if(!rst_n)

26 led <=4'b1111; //复位熄灭4个灯

27 else

28 case(state)

29 0 : begin //第一个状态点亮第一个灯,然后跳转下 一个状态

30 state <=1;

31 led <=4'b1110;

32 end

33

34 1 : begin //第2个状态点亮第2个灯,然后跳转下 一个状态

35 state <=2;

36 led <=4'b1101;

37 end

38

39 2 : begin //第3个状态点亮第3个灯,然后跳转下 一个状态

40 state <=3;

41 led <=4'b1011;

42 end

43 3 : begin //第4个状态点亮第4个灯,然后跳转0状态

44 state <=0;

45 led <=4'b0111;

46 end

47

48 default:state <=0;//否则跳转0状态

49 endcase

50

51endmodule

测试模块

0`timescale1ns/1ps//例化时标

1

2moduletb();

3

4 regclk,rst_n;

5 wire[3:0]led;

6

7 initialbegin

8

9 clk =1;

10 rst_n =0;

11

12 #200.1rst_n =1;

13

14

-

FPGA

+关注

关注

1629文章

21736浏览量

603375 -

状态机

+关注

关注

2文章

492浏览量

27541

发布评论请先 登录

相关推荐

FPGA工程师:如何在FPGA中实现状态机?

明德扬视频分享--点拨FPGA课程---第十四章 状态机设计

FPGA---如何写好状态机,详细下载pdf

一个简单的状态机设计

状态机设计

高速环境下FPGA或CPLD中的状态机设计

VHDL有限状态机设计-ST

FPGA之状态机设计原则

如何在FPGA中实现状态机

基于FPGA的状态机设计

FPGA学习系列:9.简单状态机设计

FPGA学习系列:9.简单状态机设计

评论