本设计实例中使用分立晶体管对由相关精密电阻所控制的五个三态引脚中每一个的三态加权电流(1、3、9、27、81μA)进行求和。每个阻值由其特定屈特的电流权重与施加两端的参考电压之比决定。

Trit:屈特,名词(计算),用一位表述三态,是可以有三种不同状态的基本信息单位。

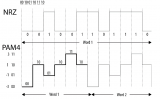

EDN主编Michael Dunn写过一篇有趣的文章“三进制DAC:分辨率更高,位数更少”(见《EDN电子技术设计》4月刊),文中探索了一个有趣的想法:从那些能够单独编程为输出和三态(即0、高阻、1,分别对应三态值0、1、2)的端口引脚,得到比通常单个比特更多的信息。从信息论的角度看,1屈特≈1.58比特,这是很有意义的,例如,只需5屈特就可获得接近8比特的分辨率。

然而,从一个资深模拟设计师的角度看,最有趣的是将理论转化为精确的输出,同时适应温度变化、单轨电源带有噪声并可变等现实世界的复杂问题。Michael的文章阐述了一些有趣方法。图1是另一种方法。

图1:三态DAC将分立晶体管与并联基准结合起来。

我的设计是使用分立晶体管对相关精密电阻所控制的五个三态引脚中每一个的三态加权电流(1、3、9、27、81µA)进行求和。每个阻值由其特定屈特的电流权重与施加其上的电压参考比决定,对于t = 0、1、2、3、4 ...,根据公式1,有:

Rt=1M•(2V − 0.06•log10(3t)) / 2V/3t (1)

读者可能看出0.06•log项是正向偏置双极结(在此为2N5087的发射极/基极结)两端电压常见的二极管公式,它对源于每个DAC屈特的不同电流的VBE产生影响。2V项来自LM4040参考,它提高了PSRR(电源抑制比)精度, 2N5089的射极跟随器阻抗耦合进其20kΩ偏置电阻会影响PSRR精度。

PSRR = 20kΩ/(26mV/120µA)=39dB (2)

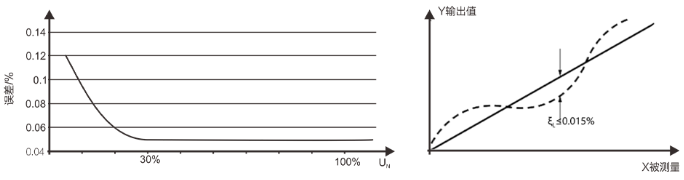

用图1中的标准值代替公式1中计算出的值就可得出图2中预测的不错的性能,包括良好的单调性、积分线性和准确性。

图2:三态DAC具有良好的线性和单一性。

图3:仔细观察积分非线性,右轴为电压。

尽管将普通的二进制输出多路复用至各种便宜且容易获得的单片DAC芯片有多种可选方法,本文还是介绍了这种可节省几个端口引脚的器件密集方法。当然,前述均不能解决其明显的实用性或性价比问题。想一想,这可能是一件好事。

或许,并非所有令人愉悦的难题一定要实用?

-

dac

+关注

关注

43文章

2272浏览量

190845 -

比特

+关注

关注

0文章

16浏览量

10488

发布评论请先 登录

相关推荐

请问aic3254可以调节比特率吗?需要涉及哪些相关的寄存器?

Amoonsky AMS-VS100:开创LED控制新纪元

VS高精度电压传感器

关于屈特 vs 比特的相关设计

关于屈特 vs 比特的相关设计

评论