有人说是负载电容,是用来纠正晶体的振荡频率用的;有人说是启振电容;有人说起谐振作用的。

电容与内部电路共同组成一定频率的振荡,这个电容是硬连接,固定频率能力很强,其他频率的干扰就很难进来了。

讲的通俗易懂一点,用一个曾经听过的笑话来比喻,大概意思就是本飞机被我劫持了,其他劫持者等下次吧。这个电容就是本次劫机者。

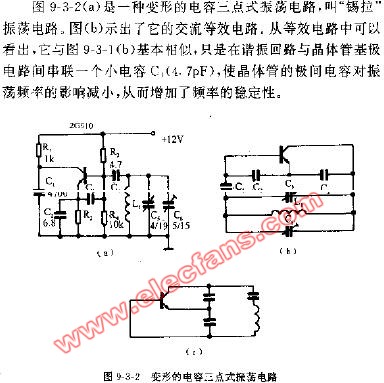

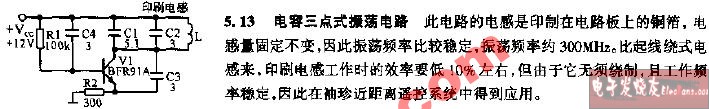

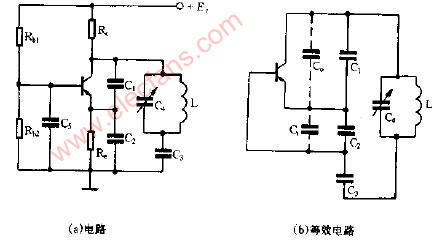

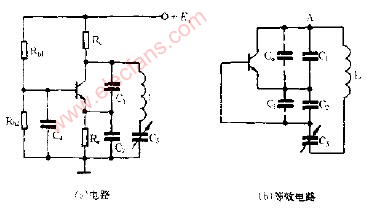

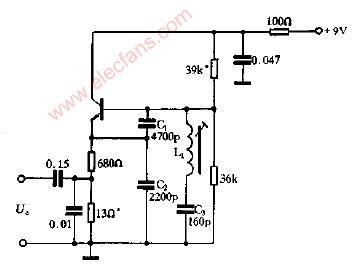

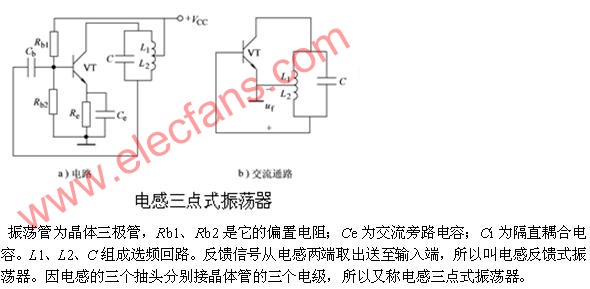

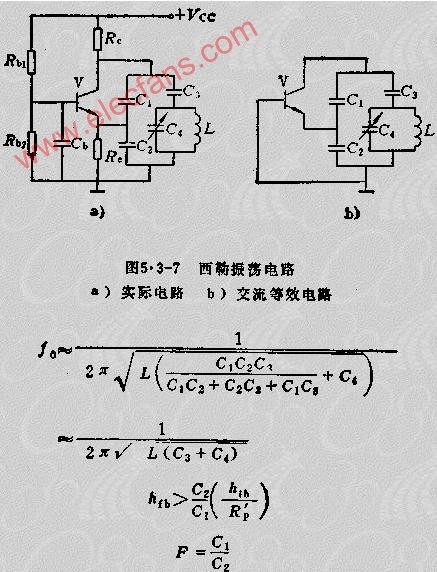

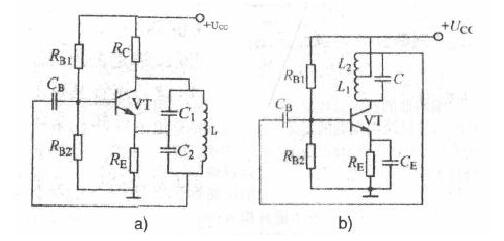

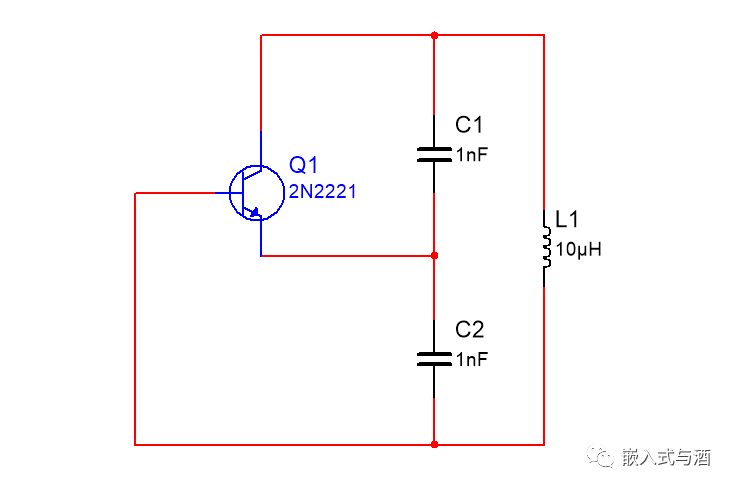

晶振电路其实是个电容三点式振荡电路,输出是正玄波晶体等效于电感,加两个槽路分压电容,输入端的电容越小,正反馈量越大。负载电容每个晶振都会有的参数,例如稳定度是多少PPM,部分人会称之为频差,单位都是PPM,负载电容是多少PF等。当晶振接到震荡电路上在震荡电路所引入的电容不符合晶振的负载电容的容量要求时震荡电路所出的频率就会和晶振所标的频率不同

再举例说明

一个4.0000MHz+-20PPM负载电容是16PF的晶振当负载电容是10PF时震荡电路所出的频率就可能会是4.0003MHz当负载电容是20PF时震荡电路所出的频率就可能会是3.9997MHz

在一些对频率精度要求高的电路上如PLL的基准等。。。就是并多个可调电容来微调频率的如果对频率精度要求不高就用固定电容就行了

晶振负载电容一般有2种接法1并联在晶振上2串联在晶振上第2种比较常用2个脚都接一个电容对交流地

晶体元件的负载电容是指在电路中跨接晶体两端的总的外界有效电容。是指晶振要正常震荡所需要的电容。一般外接电容,是为了使晶振两端的等效电容等于或接近负载电容。要求高的场合还要考虑ic输入端的对地电容。应用时一般在给出负载电容值附近调整可以得到精确频率。此电容的大小主要影响负载谐振频率和等效负载谐振电阻。

晶振的负载电容=[(Cd*Cg)/(Cd+Cg)]+Cic+△C式中Cd,Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容)+△C(PCB上电容).就是说负载电容15pf的话,两边个接27pf的差不多了,一般a为6.5~13.5pF

各种逻辑芯片的晶振引脚可以等效为电容三点式振荡器. 晶振引脚的内部通常是一个反相器, 或者是奇数个反相器串联. 在晶振输出引脚XO 和晶振输入引脚 XI 之间用一个电阻连接, 对于 CMOS 芯片通常是数 M 到数十 M 欧之间.很多芯片的引脚内部已经包含了这个电阻, 引脚外部就不用接了. 这个电阻是为了使反相器在振荡初始时处与线性状态,反相器就如同一个有很大增益的放大器, 以便于起振. 石英晶体也连接在晶振引脚的输入和输出之间, 等效为一个并联谐振回路,振荡频率应该是石英晶体的并联谐振频率. 晶体旁边的两个电容接地, 实际上就是电容三点式电路的分压电容, 接地点就是分压点.以接地点即分压点为参考点, 振荡引脚的输入和输出是反相的, 但从并联谐振回路即石英晶体两端来看, 形成一个正反馈以保证电路持续振荡.在芯片设计时, 这两个电容就已经形成了, 一般是两个的容量相等, 容量大小依工艺和版图而不同, 但终归是比较小,不一定适合很宽的频率范围. 外接时大约是数 PF 到数十 PF, 依频率和石英晶体的特性而定. 需要注意的是:这两个电容串联的值是并联在谐振回路上的, 会影响振荡频率. 当两个电容量相等时, 反馈系数是 0.5, 一般是可以满足振荡条件的,但如果不易起振或振荡不稳定可以减小输入端对地电容量, 而增加输出端的值以提高反馈量.

设计考虑事项:

1.使晶振、外部电容器(如果有)与 IC之间的信号线尽可能保持最短。当非常低的电流通过IC晶振振荡器时,如果线路太长,会使它对EMC、ESD与串扰产生非常敏感的影响。而且长线路还会给振荡器增加寄生电容。2.尽可能将其它时钟线路与频繁切换的信号线路布置在远离晶振连接的位置。3.当心晶振和地的走线4.将晶振外壳接地如果实际的负载电容配置不当,第一会引起线路参考频率的误差.另外如在发射接收电路上会使晶振的振荡幅度下降(不在峰点),影响混频信号的信号强度与信噪.当波形出现削峰,畸变时,可增加负载电阻调整(几十K到几百K).要稳定波形是并联一个1M左右的反馈电阻.

-

电容

+关注

关注

100文章

6039浏览量

150299 -

振荡器

+关注

关注

28文章

3832浏览量

139058 -

晶体

+关注

关注

2文章

1352浏览量

35419

原文标题:晶振旁边接的两个电容是起什么作用

文章出处:【微信号:weixin21ic,微信公众号:21ic电子网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

晶振电路其实是个电容三点式振荡电路

晶振电路其实是个电容三点式振荡电路

评论