声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1634文章

21829浏览量

607940

发布评论请先 登录

相关推荐

基于FPGA显示数字钟

用Verilog HDL语言实现,通过VGA在LCD显示针式数字钟,像windows右下角 日期和时间 属性那个钟那样。我想问的是如何从RAM里读取各个图片然后显示出来,或通过改变图片属性来达到每秒刷新一下各针的位置

发表于 09-25 09:31

基于FPGA Vivado的流水灯样例设计资料分享

【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

发表于 02-07 08:02

基于FPGA设计实现一个多功能数字钟相关资料分享

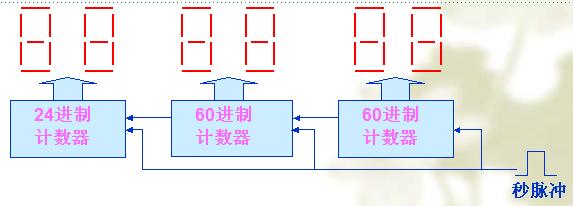

1、基于FPGA设计实现一个多功能数字钟在FPGA中设计实现一个多功能数字钟,具备以下功能:准确计时。能显示时、分、秒,小时的计时为24进制,分和秒的计时为60进制。校时功能。时、分可

发表于 07-08 17:26

基于 FPGA Vivado 的数字钟设计(附源工程)

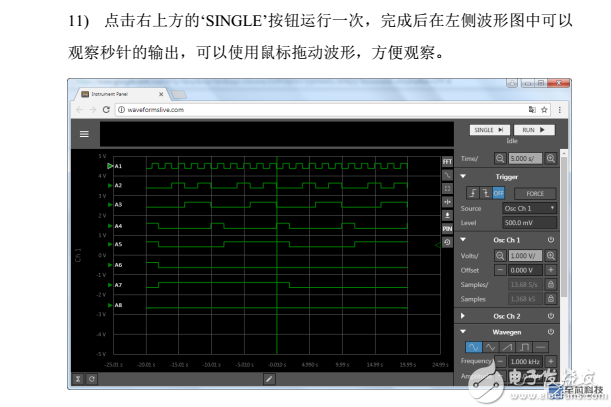

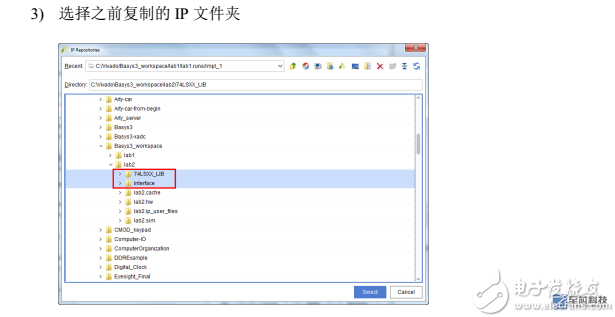

今天给大侠带来基于 FPGA Vivado 的数字钟设计,开发板实现使用的是Digilent basys 3。话不多说,上货。

需要源工程可以在以下资料获取里获取。

资料汇总|FPGA

发表于 08-18 21:18

多功能数字钟的设计与实现

多功能数字钟的设计与实现一、实验目的 1.掌握数字钟的设计原理。 2.用微机实验平台实现数字钟。 3.分析比较微机实现的数字钟和其他方法实现的数

发表于 05-03 11:38

•477次下载

基于FPGA和Quartus II的多功能数字钟设计与实现

本文以FPGA平台为基础,在QuartusⅡ开发环境下设计开发多功能数字钟。数字钟实现计时\校时\整点报时\世界时钟功能.

发表于 12-18 11:51

•3.8w次阅读

基于fpga的数字钟设计的两款方案(含程序)

以FPGA平台为基础,采用VHDL语言在QuartusⅡ开发环境下设计开发多功能数字钟,具有计时、校时、蜂鸣闹铃的功能.

发表于 11-07 12:01

•3.3w次阅读

fpga数字钟介绍_fpga数字钟设计

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定,通常使用石英晶体振荡器电路构成数字钟。

发表于 01-15 15:37

•1.1w次阅读

【FPGA Vivado】基于 FPGA Vivado 的流水灯样例设计

【流水灯样例】基于 FPGA Vivado 的数字钟设计前言模拟前言Vivado 设计流程指导手册——2013.4密码:5txi模拟

发表于 12-04 13:21

•26次下载

FPGA多功能数字钟系统原理

FPGA(可编程逻辑门阵列)是一种集成电路芯片,具有可编程的数字逻辑功能。多功能数字钟系统利用FPGA技术实现了时钟的显示、计时、报时等功能。本文将详细介绍

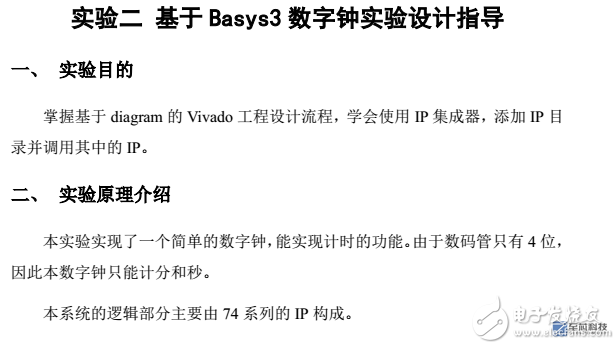

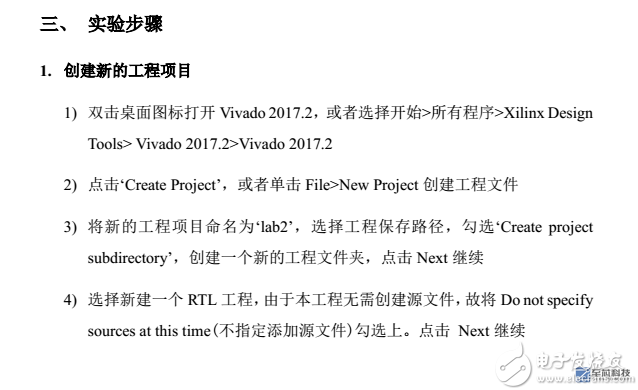

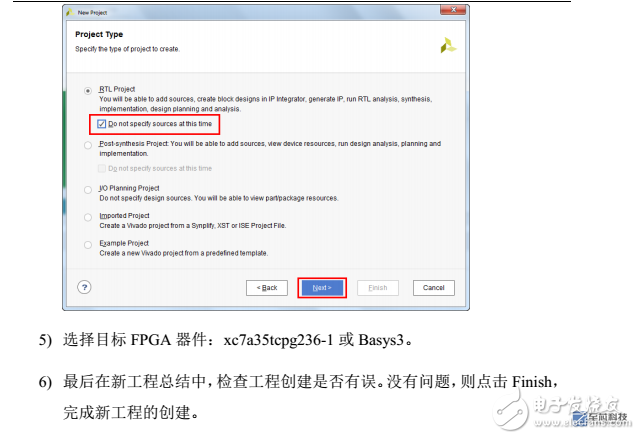

基于FPGA vivado 17.2 的数字钟设计

基于FPGA vivado 17.2 的数字钟设计

评论