声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

553文章

7998浏览量

348869 -

ti

+关注

关注

112文章

8115浏览量

212400 -

Cache

+关注

关注

0文章

129浏览量

28342

发布评论请先 登录

相关推荐

请问C6748分别在simu和emu下调用运算库DSP_dotprod,cycle数不对,emulation下慢4倍,这是为什么?

支持C67芯片,不知道C64的库是不是全支持,现在运算结果是正确的)DSP_dotprod.h中说cycle=N/4+16,在CCS5.4的

发表于 06-21 06:21

C6000 DSP二级cache的工作机理,是不是说,代码段.text中的指令要从DDR或者SDRAM中被搬运或者映射到L1P cache中才能被执行?

本帖最后由 一只耳朵怪 于 2018-6-22 14:18 编辑

关于C6000 DSP 二级cache的工作机理有一些问题,像和大家讨论下。谢谢!cpu一上电,就要开始一条条的

发表于 06-22 02:29

在DSP/BIOS想将L2的64k配置成cache,请问需要怎么操作?

您好,我使用的芯片是C6748,使用DSP/BIOS。C6748的L1P L1D L2都可以部分配置成缓存或RAM。

发表于 08-02 06:54

AVS变换算法在C64x+DSP上的实现

讨论了音视频编码标准AVS 中比较耗时的部分——8x8 IDCT 变换的一维快速算法,提出了变换算法在TI 公司的TMS320DM6446 芯片的C64x+ DSP 子系统上的快速实现

发表于 08-24 08:38

•10次下载

TI C64XX DSP特点及线性汇编程序分析

TI C64XX DSP特点及线性汇编程序分析

TI的DSP C64XX系列的EMIF口是否能在不同的CE空间挂两种不同的同步器件请教一个

发表于 04-07 10:48

•36次下载

采用Linux内核的C64x系列(TI)

采用Linux内核的C64x系列(TI)

德州仪器 (TI) 推出为其 C64x 系列数字信号处理器 (DSP) 与多内核片

发表于 05-11 17:29

•1402次阅读

32位DSP两级cache的结构设计

本文参照计算机存储结构,利用虚拟存储技术,对存储系统的结构进行了改进。在DSP中引入二级Cache存储器结构,在较小的硬件开销下提高了

发表于 12-10 16:25

•2216次阅读

TMS320C64x+ DSP 大字节DSP库 程序员参考

TMS320C64x + TMS320C64X数字信号处理器(DSP)的TMS320C6000系列DSP

发表于 04-13 16:55

•7次下载

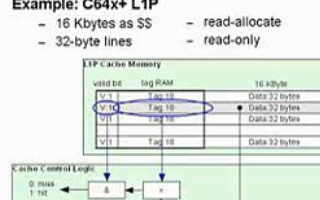

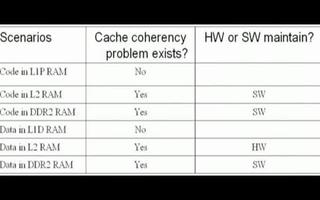

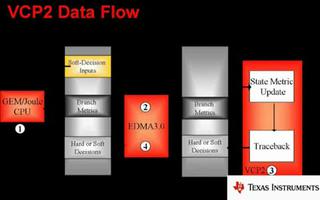

基于c64+的DSP芯片的特点

此次培训课程,会让您了解到,基于c64+的DSP芯片,能满足电信,医疗,视频处理应用领域中,高性能DSP的需求。由DSP高性能部门技术支持工程师为您全程指导,敬请观看。

TMS320C64x在高性能DSP应用中的高速缓存使用情况

电子发烧友网站提供《TMS320C64x在高性能DSP应用中的高速缓存使用情况.pdf》资料免费下载

发表于 10-21 09:43

•0次下载

DSP上Cache 在 C64+ 系列中的应用(1)

DSP上Cache 在 C64+ 系列中的应用(1)

评论