声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21729浏览量

602971 -

DDR3

+关注

关注

2文章

276浏览量

42240 -

Altera

+关注

关注

37文章

781浏览量

153919

发布评论请先 登录

相关推荐

FPGA和DDR3 SDRAM DIMM条的接口设计实现

更快、更大,每比特的功耗也更低,但是如何实现FPGA和DDR3 SDRAM DIMM条的接口设计呢? 关键字:均衡(leveling)如果FPGA

发表于 04-22 07:00

DDR3存储器接口控制器IP助力数据处理应用

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA

发表于 05-24 05:00

基于DDR3存储器的数据处理应用

了设计的一大挑战。FPGA可通过在单个FPGA中实现多个视频处理器来提供强大的处理能力。那么现在的挑战就变成了要使数据尽快且高效地从FPGA

发表于 05-27 05:00

与Kintex 7的DDR3内存接口

& 14用于DDR3内存接口,但由于我使用的是3.3V的fash存储器IC,我必须使用bank 14进行闪存存储器接口。原因是需要的

发表于 04-17 07:54

基于Stratix III的DDR3 SDRAM控制器设计

本文介绍了DDR3 SDRAM 的基本特点和主要操作时序,给出了一种基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的设计方法。详述了控制器

发表于 07-30 17:13

•30次下载

DDR3存储器接口控制器IP核在视频数据处理中的应用

DDR3存储器系统可以大大提升各种数据处理应用的性能。然而,和过去几代(DDR和DDR2)器件相比,DDR3

发表于 07-16 10:46

•1848次阅读

基于FPGA的DDR3用户接口设计技术详解

本文详细介绍了在Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核实现高速率DDR3芯片控制的设计思想和设计方案。针对高速

发表于 11-17 14:26

•2.5w次阅读

基于FPGA的DDR3多端口读写存储管理的设计与实现

为了解决视频图形显示系统中多个端口访问DDR3的数据存储冲突,设计并实现了基于FPGA的DDR3存储

发表于 11-18 18:51

•7132次阅读

FPGA如何与DDR3存储器进行正确的数据对接?

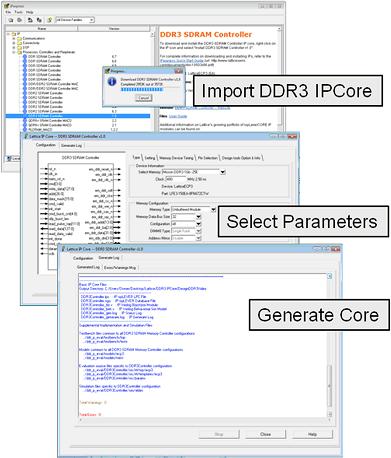

,如屏幕上所示。

为了更好地进行演示,我们将使用这里所示的Stratix III DDR3存储器电路板。它上面有几个高速双倍数据速

Stratix III FPGA的特点及如何实现和高速DDR3存储器的接口

Stratix III FPGA的特点及如何实现和高速DDR3存储器的接口

评论