声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22502浏览量

639189 -

Altera

+关注

关注

37文章

828浏览量

159128

发布评论请先 登录

相关推荐

热点推荐

请问FPGA 中PLL时钟的问题

请问,想通过FPGA的PLL倍频产生个500MHz的时钟来使用,以此时钟来做定时精密延迟,不知道PLL倍频倍数有什么要求,比如好像有的器件支

发表于 01-03 17:04

MAX 10 FPGA的特性

10月1日正式开始提供的MAX 10 FPGA的一些特性,我们也来探究一下它是否真的“实至名归”。图1 Altera公司产品营销资深总监Pa

发表于 07-01 08:14

请问FPGA PLL产生的时钟信号和AD9779A的数据时钟信号的相位关系?

你们好,

我们正在使用AD9779A进行设计,有如下疑问:

(1) 使用AD9779A的数据时钟信号(DATACLK)作为FPGA内部PLL的参考时钟,再用

发表于 12-20 07:12

Xilinx FPGA普通IO作PLL时钟输入

普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";

发表于 02-09 12:54

•7742次阅读

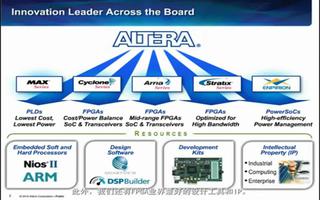

Altera® MAX® 10 FPGA介绍(特性、优势、电路图)

控制面板,汽车电子,工业控制和消费类电子产品.本文介绍了Altera MAX 10 FPGA主要优势,Altera MAX 10

发表于 05-22 10:11

•6425次阅读

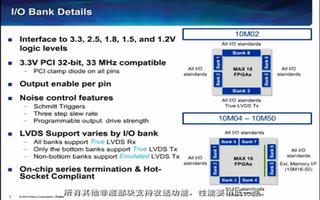

MAX 10 FPGA GPIO的特点优势

MAX 10 FPGA GPIO培训,可编程逻辑一般用作胶合逻辑,连接电路板上的大量数字逻辑器件,这些器件通常有不同的I/O标准、电压电平和协议。这里列出了我们I/O

FPGA设计:PLL 配置后的复位设计

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL

发表于 03-29 17:19

•3451次阅读

用FPGA的锁相环PLL给外围芯片提供时钟

用FPGA的锁相环PLL给外围芯片提供时钟 FPGA锁相环PLL(Phase-Locked Loop)是一种广泛使用的

FPGA的时钟电路结构原理

FPGA 中包含一些全局时钟资源。以AMD公司近年的主流FPGA为例,这些时钟资源由CMT(时钟管理器)产生,包括DCM、

发表于 04-25 12:58

•3544次阅读

浅谈FPGA的时钟输入要求

Virtex-7 FPGA的时钟输入主要通过其全局时钟缓冲器(BUFG、BUFH等)和时钟管理模块(MMCM、PLL)来处理。对输入

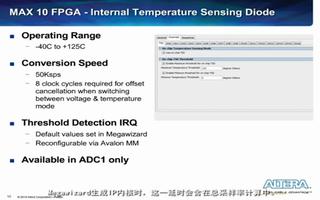

关于MAX 10 FPGA PLL和时钟特性选项的培训

关于MAX 10 FPGA PLL和时钟特性选项的培训

评论