声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

561文章

8277浏览量

368464 -

ti

+关注

关注

114文章

8085浏览量

220096 -

多核

+关注

关注

0文章

43浏览量

12719

发布评论请先 登录

相关推荐

热点推荐

ADI推出Blackfin和SHARC处理器的下一代软件开发平台CCES

ADI全球领先的高性能信号处理解决方案供应商,最近推出适用于Blackfin®和SHARC®处理器的下一代软件开发平台CrossCore® Embedded Studio (CCES)。

发表于 09-24 08:57

•2605次阅读

2016CES:Atmel下一代触摸传感技术亮相

2016年1月7日——全球微控制器(MCU)及触控技术解决方案领域的领导者Atmel公司今日宣布,将把下一代压力传感技术应用于最新面向智能

发表于 01-13 15:39

消费电子助力SoC发展,多核技术是焦点

的Cell就是一枚拥有9个处理器核心的多核处理器。如果你和处理器内核供应商Tensilica公司总裁兼首席执行官Chris Rowen博士谈

发表于 06-21 06:19

SecurCore(可靠内核技术)系列微处理器有哪些特点 主要应用哪些领域

SecurCore 系列微处理器除了具有 ARM 体系结构各种主要特点外,在系统安全方面具有 如下特点。带有灵活的保护单元,确保操作系统和应用数据的安全。采用软内核技术,防止外部对其进行扫描探测。可

发表于 09-26 09:47

高通下一代手机处理器3D与视频性能展示

高通下一代手机处理器3D与视频性能展示

来自Armdevices网站的报道,高通公司日前展示了其下一代智能手机平台MSM7X30,整体性能有了很大提升。早在去年11月高通就公布

发表于 03-04 12:03

•960次阅读

美成功破解下一代多核微处理器储存瓶颈

直写高速缓存(direct-write cache memories)是今日微处理器的支柱,因为它们能以一种对应用程序透明化的模式降低存储延迟。不过,先进处理器的设计工程师正致力于针对下一

发表于 04-25 14:55

•1584次阅读

在 TI 高性能的 DSP中,多核适应下一代处理器领域的研究和探索

探讨现今TI 在高性能 DSP,多核及适应于未来发展趋势的下一代处理器领域的研究和探索。

Intel多核微处理器技术

多核处理器是指在一枚处理器中集成两个或多个完整的计算引擎(内核)。多核技术的开发源于工程师们认识到,仅仅提高单核芯片的速度会产生过多热量且无

发表于 04-09 09:33

•9次下载

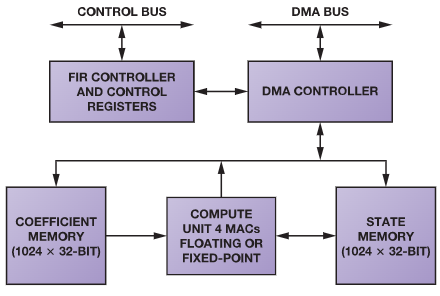

硬件加速器提升下一代SHARC处理器的性能

SHARC ADSP-2146x处理器集成了硬件加速器,可实现三种广泛使用的信号处理操作:FIR(有限脉冲响应)、IIR(无限脉冲响应)和FFT(快速傅里叶变换)。加速器卸载了核心

研究和探索下一代处理器领域的多核技术

研究和探索下一代处理器领域的多核技术

评论