声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1631文章

21806浏览量

606722 -

Altera

+关注

关注

37文章

788浏览量

154317 -

SEU

+关注

关注

0文章

12浏览量

13758

发布评论请先 登录

相关推荐

BeMicro Max 10 FPGA评估板购买问题

有谁需要BeMicro Max 10 FPGA评估板吗,本人想入手一块板子,但是联系了国内好多卖家,但均没有答复,因此决定直接arrow美国官网购买,感兴趣的朋友可以联系我,一起购买,QQ:674695298

发表于 12-15 12:45

MAX 10 FPGA的特性

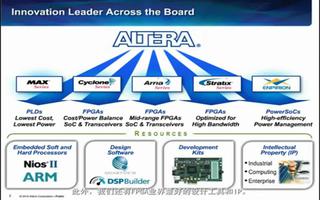

了3款足够“有料”的FPGA及SoC系列:Arria 10、Stratix 10以及MAX 10,它们都是Altera在创新大潮中重磅推出的

发表于 07-01 08:14

怎么设计抗SEU存储器电路的FPGA?

包括单粒子翻转(SEU)、单粒子闩锁(SEL)和单粒子烧毁(SEB)等三种类型,其中以SEU最为常见。在各种辐射效应当中,存储器对SEU最为敏感,所以,对存储器的抗辐射设计首先要考虑的就是抗S

发表于 08-22 07:09

如何减轻SEU对Artix-7 FPGA的影响

据我所知,Xilinx建议采用SEM来减轻SEU对7系列FPGA的影响。但Artix-7 FPGA不支持ISE 14.2中的SEM,这与Xilinx的建议(http://www.xilinx.com

发表于 07-14 07:01

MAX II器件实现FPGA设计安全解决方案

本文提供的解决方案可防止FPGA设计被拷贝,即使配置比特流被捕获,也可以保证FPGA设计的安全性。通过在握手令牌由MAX II器件传送给FPGA

发表于 01-29 16:23

•1428次阅读

艾睿电子推出针对Altera非易失性Max 10 FPGA的评估板

在Altera的MAX®10现场可编程门阵列(FPGA)系列发布之际,艾睿电子公司(NYSE:ARW)推出了BeMicro Max 10FPGA

发表于 10-08 09:58

•2596次阅读

ADC Convertor Using the MAX 10 FPGA Development Kit

ADC_Convertor_Using_MAX_10_FPGA_Development_Kit

发表于 12-07 18:20

•9次下载

采用MAX-10-FPGA替代您的MCU的七个主要原因_白皮书

本白皮书介绍使用 MAX® 10 FPGA 和 Nios® II 嵌入式处理器来替代基于微控

制器的解决方案的优势所在。超越传统的低成本 FPGA,

发表于 01-06 10:22

•39次下载

分析芯片内部不同硬件资源对于SEU效应敏感性的问题

本文重点分析芯片内部不同硬件资源对于SEU效应敏感性的问题。以SRAM型FPGA为研究对象,设计进行了两种颗粒度不同的故障注入实验。结果表明,在FPGA内部资源中,Slice资源对于SEU

发表于 11-16 19:58

•3466次阅读

介绍MAX 10 FPGA开发套件的特点性能

Altera 的 55 nm MAX® 10 FPGA 提高了外部系统组件功能的集成度,从而降低了系统级成本。与 CPLD 不同,MAX 10

介绍MAX 10 FPGA的特性及优点

此次培训比较详细介绍MAX 10系列,包括其特性和优点,高层体系结构,以及密度和封装产品等。此外,我们还有FPGA业界最好的设计工具和IP。它结合了这里列出的很多FPGA特性以及非易失

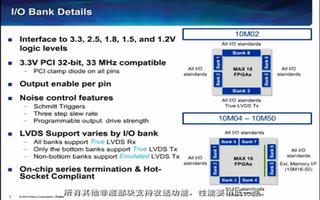

MAX 10 FPGA GPIO的特点优势

MAX 10 FPGA GPIO培训,可编程逻辑一般用作胶合逻辑,连接电路板上的大量数字逻辑器件,这些器件通常有不同的I/O标准、电压电平和协议。这里列出了我们I/O特性的很多优势。MAX

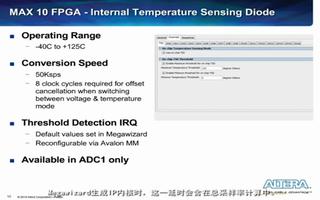

简述 MAX 10 FPGA 的设计安全和如何减小SEU

简述 MAX 10 FPGA 的设计安全和如何减小SEU

评论