声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Altera

+关注

关注

37文章

777浏览量

153852 -

内存模型

+关注

关注

0文章

7浏览量

6133

发布评论请先 登录

相关推荐

利用RLDRAM II存储器提高网络设备性能

随着语音、数据、视频流的逐渐融合,下一代网络(NGN)设计和新的宽带平台必须能在严格的带宽和时延条件下提供更强的系统性能。而RLDRAM II存储器采用专门针对高速运算进行优化的8个内存组(Bank

发表于 10-08 15:45

通过VeriStand加载MATLAB模型到实时仿真机,VeriStand出现卡顿现象

软件版本:NI VeriStand 2016运行环境:Windows7 旗舰版 SP1宿主机配置:i7处理器,8G内存,固态盘仿真机配置:i5处理器,4G内存,固态盘实时

发表于 06-09 10:28

给Altera Arria 10 FPGA和Arria 10 SoC供电:经过测试和验证的电源管理解决方案

)、更改功率额定值、计算效率和功率损耗、进行每个电源模块的仿真、选择 DC/DC 稳压器的型号、并认证一款定制的解决方案。LTpowerPlanner 可针对 Arria 10 开发套件的 FPGA

发表于 10-29 17:01

在Arria 10 PCI Express中更改串行和PIPE仿真的方法

如何在Arria 10 PCI Express (PCIe)中更改串行(Serial)和PIPE仿真

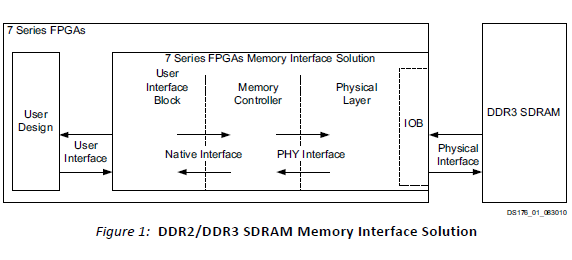

Zynq-7000 SoC和7系列FPGA设备内存接口解决方案资料说明

Xilinx Zynq-7000 SOC和7系列FPGA内存接口解决方案核心提供了到DDR3和DDR2 SDRAM、QDR II+SRAM、RLDRAM II/RLDRAM

发表于 02-25 17:24

•18次下载

英特尔Arria 10 FPGA的应用之路

中,小编为大家分别总结了英特尔 Cyclone FPGA和英特尔 Stratix 10 FPGA的应用之路,今天就轮到咱们的英特尔 Arria 10 FPGA了~ 英特尔 Arria

jvm内存模型和内存结构

JVM(Java虚拟机)是Java程序的运行平台,它负责将Java程序转换成机器码并在计算机上执行。在JVM中,内存模型和内存结构是两个重要的概念,本文将详细介绍它们。 一、JVM

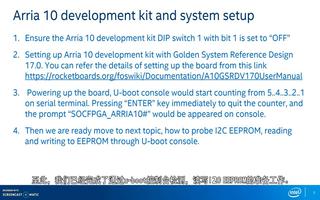

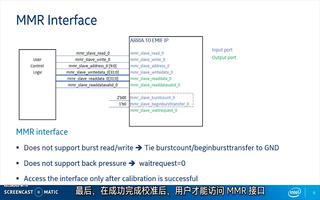

厂商内存模型运行 Arria 10 RLDRAM3 的仿真操作

厂商内存模型运行 Arria 10 RLDRAM3 的仿真操作

评论