- Load:0 second

- Duration:0 second

- Size:0x0

- Volume:0%

- Fps:61fps

- Sudio decoded:0 Byte

- Video decoded:0 Byte

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

锁相环

+关注

关注

35文章

590浏览量

87965 -

Altera

+关注

关注

37文章

790浏览量

154378

发布评论请先 登录

相关推荐

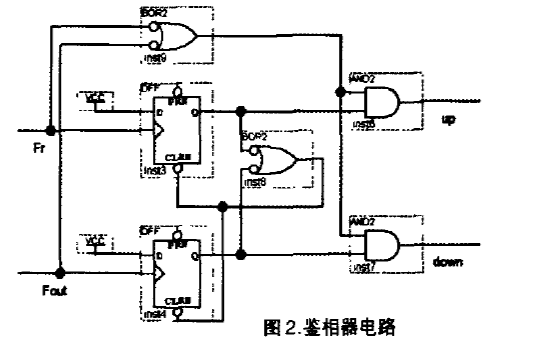

锁相环动态频相跟踪特性分析

在分析锁相环工作原理的基础上,利用传递函数法建立了锁相环跟踪误差的二阶等效模型,并对锁相环的动态频相跟踪特性进行了理论分析.利用MATLAB

发表于 03-01 18:14

•32次下载

锁相环技术在频率跟踪中的应用研究

本文介绍锁相环及其频率跟踪的基本原理,给出二阶锁相环和四阶锁相环的设计依据。在此基础上,对四阶锁相环实现频率跟踪的转换时间进行了仿真,就如何

发表于 07-29 16:28

•43次下载

使用PLD内部锁相环解决系统设计难题

摘要: 从整个应用系统的角度,理解和分析PLD内部锁相环;在此基础上,深入剖析锁相环的相移结构,同时用这个技术解决系统设计难题。

关键

发表于 06-20 12:40

•799次阅读

锁相环在相位检测中的应用

锁相环在相位检测中的应用 锁相环(PLL)是一种电子技术中广泛应用的电路,用于调整一个输出信号的相位来精确匹配一个参考信号。锁相环

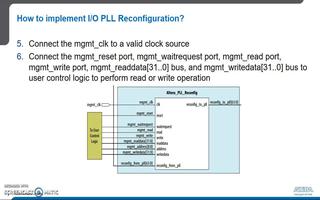

在 Arria 10 中实现 I/O 锁相环动态相移的方法

在 Arria 10 中实现 I/O 锁相环动态相移的方法

评论