声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1631文章

21806浏览量

606681 -

IO

+关注

关注

0文章

467浏览量

39444 -

Altera

+关注

关注

37文章

788浏览量

154315

发布评论请先 登录

相关推荐

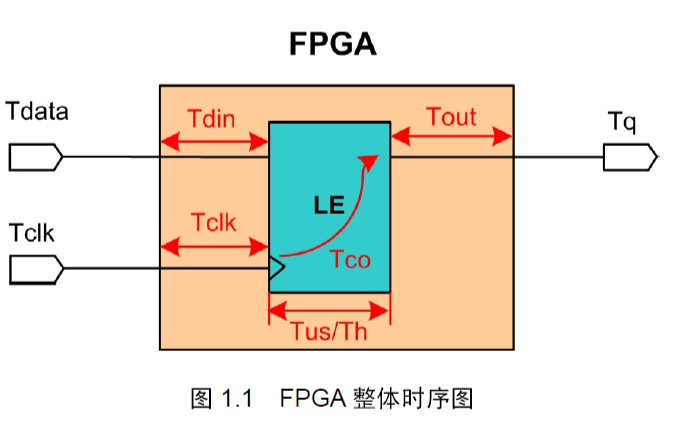

FPGA 高级设计:时序分析和收敛

今天给大侠带来FPGA 高级设计:时序分析和收敛,话不多说,上货。

这里超链接一篇之前的STA的文章,仅供各位大侠参考。

FPGA STA(静态

发表于 06-17 17:07

FPGA静态时序分析——IO口时序(Input Delay /output Delay)

FPGA静态时序分析——IO口时序(Input Delay /output Delay)1.1概述 在高速系统中

发表于 04-25 15:42

FPGA高级时序综合教程

FPGA高级时序综合教程The UCF FileUCF =用户约束文件( User Constraints File )可以用文本编辑器和XilinxConstraints Editor (GUI

发表于 08-11 11:28

如何有效的管理FPGA设计中的时序问题

如何有效的管理FPGA设计中的时序问题

当FPGA设计面临到高级接口的设计问题时,EMA的TimingDesigner可以简化这些设计问题

发表于 04-15 14:19

•727次阅读

FPGA中的时序约束设计

一个好的FPGA设计一定是包含两个层面:良好的代码风格和合理的约束。时序约束作为FPGA设计中不可或缺的一部分,已发挥着越来越重要的作用。毋庸置疑,

发表于 11-17 07:54

•2610次阅读

关于 FPGA 中的高级 IO 时序

关于 FPGA 中的高级 IO 时序

评论