0 引言

雷达导引头是反辐射导弹(ARM)的关键部件,被誉为ARM的“眼睛”,主要功能是完成对辐射源的分选、截获和跟踪,其技术性能将直接影响反辐射导弹的作战性能[1]。随着雷达技术的提高,超宽频带导引头进一步扩大频率覆盖范围,使反辐射导弹几乎能覆盖所有频段的各种辐射源[2]。传统导引头在分选识别多频带辐射源时,一般流程是AD采样处理后直接传送超宽带频谱至数字信号处理部分,再对宽带数据进行抽取和滤波。随着导引头频率覆盖范围的进一步扩大,传统处理流程不仅会造成效费比总体偏低[3],而且传统并行LVDS传输接口存在大量数据连线复杂[4]等难题,难以迎合现代反辐射导引头宽频带、小型化的发展趋势。

为了提高导引头总体效费比,简化其物理互联以趋向小型化,提出了一种基于DDC模块和JESD204B接口的导引头接收电路设计方案。一方面,通过ADC内置的DDC模块对数字化后的宽带数据进行筛选、抽取和滤波之后再传送给信号处理部分,提高了导引头对多种频带雷达信号的处理效费比;另一方面,采用JESD204B高速串行接口作为数字信号传输接口,在保证单通道数据传输速度的同时,极大地简化了数据连线复杂度,为系统小型化设计奠定了基础。

1 方案设计

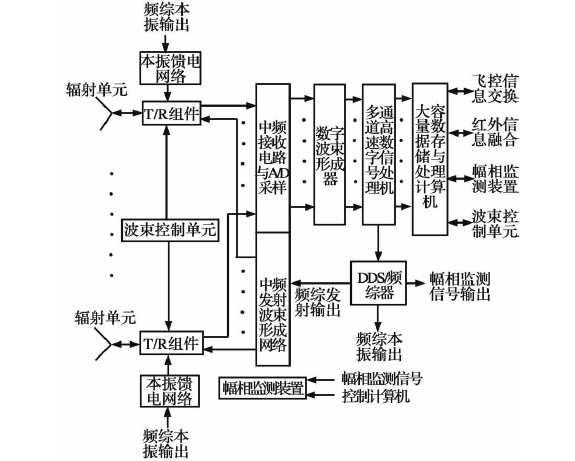

典型被动雷达导引头由天线、接收机、信号分选与选择系统、指令控制放大器等组成[5]。图1是16通道导引头接收系统框图。超宽频带接收天线接收超宽频带雷达辐射信号,传输至射频信号调理电路,射频信号调理电路的作用是防止接收辐射信号中噪声、杂波影响模数转换器的转换精度。模数转换器将输入模拟信号进行采样转换成数字信号,再由模数转换器所带的DDC模块进行抽取和滤波,最后通过JESD204B高速接口送给数字信号处理电路,通常是带JESD204B接口的高性能FPGA。该系统的导引头接收电路由16通道的射频信号调理电路,8片带DDC模块和JESD204B接口的双通道模数转换器以及8片带JESD204B接口的FPGA组成。

1.1 高速模数转换芯片ADC32RF45

设计的反辐射导引头接收电路选择采用美国TI公司的双通道、14位3.0GSPS模数转换芯片ADC32RF45,支持输入频率高达4 GHz及以上的射频(RF)采样,并且模拟单通道能够同时处理并输出带宽为75 MHz~600 MHz范围内的双基带信号。如图2所示,其内部集成了模拟信号缓冲模块、高速14位ADC、自动增益控制模块、数字下变频模块和JESD204B接口模块。

1.2 片上数字下变频器

片上数字下变频器由混频器、数控振荡器和抽取滤波器3部分组成,其结构框图如图3所示,主要功能是从采样转换输出的高速宽带信号中提取到基带信号,同时对基带信号进行抽取和滤波,降低信号速率,以满足后续模块的实时处理[6]。本文中所采用ADC的每条模拟通道后面都有一组数字下变频器,可以在单通道模拟载波输入中实现双基带信号提取与处理。

1.3 JESD204B接口

ADC32RF45的数字输出接口为JESD204B子类1接口,模拟单通道最高同时支持四路链路,每一条传输链路带宽最高为12.5 Gbps。ADC32RF45芯片中的JESD204B接口的单模拟通道输出链路数取决于前端采样率和总抽取阶数的配置,可以被配置为1线、2线和4线模式。

2 系统设计与应用

本文中反辐射导引头系统以TI公司模数转换芯片ADC32RF45作为导引头接收电路核心,采用赛灵思K7系列FPGA作为后端数字信号处理单元,通过软件仿真和实验测试验证了基于数字下变频处理和JESD204B接口的模拟单通道接收方案的可行性与优点。

2.1 宽带接收电路设计

为了初步验证方案的可行性,设计了基于ADC32RF45接收电路,具体实现方式为将ADC32RF45开发模块与单片FPGA开发套件通过专用连接插件相连。该接收电路采用FPGA作为数字信号处理中心,利用其内部高速收发器GTX实现了JESD204B接口,使得FPGA完成了对模拟前端ADC32RF45单路输出数据的接收。

2.2 数字下变频器应用分析

在高速采集系统中,高采样率和输入带宽的ADC为后端数字信号处理单元提供了较宽的可见频谱[7]。在以往的数字下变频结构设计中,很少在考虑多级滤波器设计的同时,引入多带宽设计的思路来扩展数字下变频器的适用范围[8]。针对反辐射导引头工作特点,需要实时检测多个窄带数据以实现对多种型号雷达的制导攻击,本文采用片上数字下变频器实现了对多带宽基带信号的筛选、抽取与滤波。

ADC数字化后的多频带复合射频信号对应两条下变频链路,分别乘以两个零相位、频率为目标频带中心频率的正弦信号,将感兴趣频带中心变频到零赫兹。在将感兴趣带宽信号降频之后,再通过带有抽样功能的低通滤波器滤去不需要的频率成分,保留感兴趣且对后续信号处理有用的频段信息,使得后端资源利用率得到优化。

2.3 JESD204B接口应用分析

当前并行输入/输出技术存在带宽限制,例如CMOS或LVDS,迫使数据转换器的管脚数目越来越多[9]。当导引头接收电路实现多频带采样处理功能,应用并行LVDS接口不仅难以负荷高达吉赫兹的瞬时带宽,而且使得模拟前端与后端FPGA之间连线布局复杂。为了提高数据传输速率,降低导引头内部电路复杂度,使导引头整体趋向小型化,本设计采用JESD204B协议。JESD204协议于2006年首次提出,仅支持单一通道的数据传输,传输速度为3.125 Gb/s,其升级版JESD204A 协议增加了对多路串行通道传输的支持能力,而最新版JESD204B增加了对确定延时的条款并将传输速度进一步提高到了12.5 Gb/s[10]。链路建立及传输具体流程图如图4所示。

本设计以赛灵思公司免费的基于GTX的JESD204 PHY IP核作为设计基础,使用VIVADO软件设计上层硬件逻辑。JESD204B链路间同步分为三个阶段,字同步、帧同步和数据传输。在字同步阶段,FPGA使用GTX中的时钟数据恢复技术从ADC输出数据流中定位控制字。在帧同步阶段,为了对齐所有链路,作为接收方,FPGA需要检验链路参数和通过系统参考信号建立帧数据与多帧数据边界。在数据传输阶段,本设计通过FPGA内部逻辑设计实现了数据流中控制字符的替换,完成原始数据还原。

3 测试结果与分析

3.1 JESD204B接口测试

利用Xilinx提供的Integrated Bit Error Ratio(IBERT)对高速串行通信测试,不仅使测试更加方便快捷,更有利于快速检测、改善FPGA板卡上高速吉比特收发器的通信质量[11]。通过VIVADO软件内部误码分析眼图,“眼”睁开状态明显,误码率量级为e-9,属于正常范围,证明链路信号完整性良好。

同理,Xilinx公司的FPGA芯片具备内部逻辑分析工具,通过JATG接口实现与FPGA芯片之间数据的连接[12],通过配置使ADC进入JESD204B链路自测试模式,即在不采样的情况下ADC输出测试信号波形。通过VIVADO软件内部逻辑分析工具抓取经过单链路JESD204B接口接收的测试信号如图5所示,正弦波形显示良好,由此可证明单链路JESD204B接口可以正确解析信号。

3.2 基带筛选仿真

在默认采样率fs为3 GSPS的情况下,通过MATLAB软件验证利用两个数字下变频器从双频带载波信号提取两个基波信号方案的可行性。采用频分复用调制,利用信号发生器AMU200将带宽为50 MHz和140 MHz的基带信号分别调制到中心频率分别为400 MHz和1.2 GHz的正弦载波,模拟出经过采样转换后的双频带载波信号。仿照ADC内部下变频模块组成建立模型,设置本振频率NCO2为400 MHz和NCO1为1.2 GHz,并且每一个抽取滤波器的抽取系数为4,因此每一个数字下变频器的总抽取系数为8,经过数字下变频后输出基带信号的截止频率为0.0625×fs。将输入双基带载波信号和输出的两个基带信号分别进行快速傅里叶变换,得到如图6、图7和图8所示频谱。

由仿真图分析可知,仿照ADC内部单通道数字下变频器所建立的数字下变频模型可以实现双基带信号提取滤波功能,证明设计方案具有可行性。

4 结论

本文设计了基于数字下变频和JESD204B接口的导引头接收电路,介绍分析了数字下变频器和JESD204B接口在反辐射导引头领域的应用优势。针对反辐射导引头研制领域宽频带、多载波和小型化的发展趋势,灵活应用新型高速ADC中数字下变频器,宽带导引头接收可以输入带宽高达4 GHz,在导引头前端实现了频带筛选,能够完成75 MHz~600 MHz带宽范围内多个不同的基带信号的数字下变频,与传统方案相比,提高了后端信号处理效率。利用基于高速收发器GTX的JESD204 Phy IP实现了单通道JESD204B接收接口,与并行传输接口相比,简化了板级布局连线,同时保证了数据高速传输。经过软件功能仿真以及硬件实际测试,初步验证了方案设计的可行性,为研制宽频带、小型化反辐射导引头奠定了一定技术基础。

-

ARM

+关注

关注

134文章

9189浏览量

369956 -

模数转换

+关注

关注

1文章

218浏览量

36980 -

DDC

+关注

关注

2文章

91浏览量

37192 -

雷达导引头

+关注

关注

1文章

5浏览量

7014

发布评论请先 登录

相关推荐

怎么利用FPGA+DSP导引头信号处理FPGA?

FPGA+DSP导引头信号处理中的FPGA技术该怎么实现?

如何利用FPGA+DSP导引头信号处理?

一种通用PD导引头目标模拟器的设计

相控阵雷达导引头捷联去耦数字平台设计

相控阵雷达导引头的介绍及其数字平台设计

如何进行相控阵雷达导引头收发系统的设计

微带天线的功率容量能否满足相控阵导引头的要求?

自研国产化图像处理板在导引头的应用

可编程导引头模拟器怎么用

关于一种小型、高效反辐射导引头接收方案的设计

关于一种小型、高效反辐射导引头接收方案的设计

评论