设计背景:

在我们设计工程中我们会用到100M,500M等时钟,如果我们的晶振达不到我们就需要倍频,再上一个文档中我们了解到了分频,可是倍频我们改怎么做了,这里我们就用了altera的IP核锁相环。

今天我们将去学习简单的IP核的调用和生成。

设计原理:

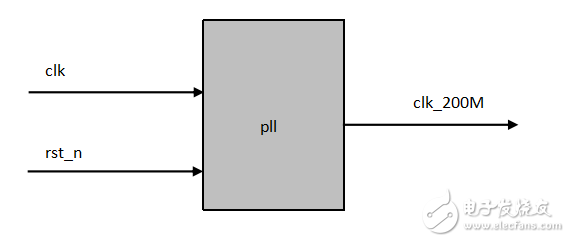

本次的设计我们调用IP核锁相环了生成一个200M的时钟,下面我们就来学习和使用简单的IP核。

设计架构图:

设计流程:

新建工程打开tools,然后选择:

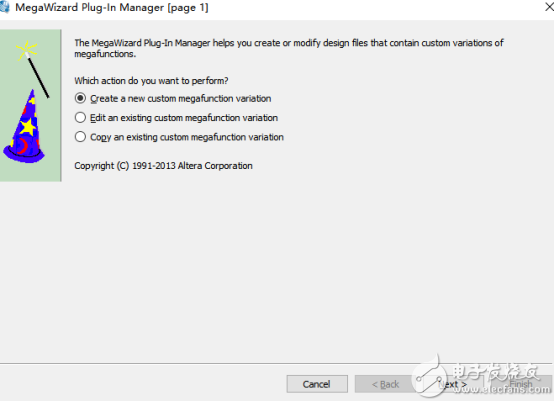

然后出现下面的界面,第一个句是建立新的IP核,第二个打开你建立好的以便于我们修改,第三个是复制一个,我们选择第一个选择,建立一个,然后下一步.

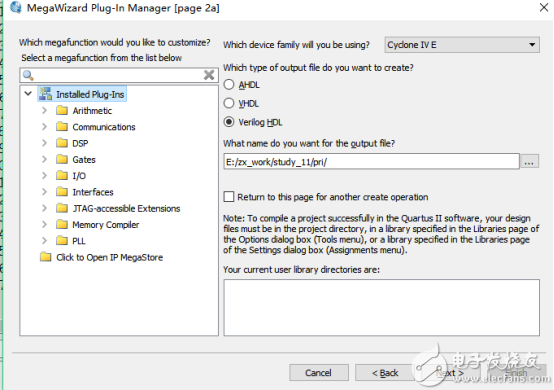

然后跳出下面的界面,我们选择下面的

然后在右边选择我们的语言verilog ,然后给我们建立的IP核起一个名字。

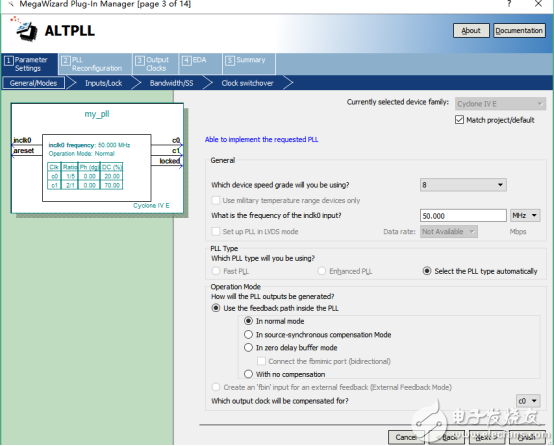

然后跳出下面的界面,inclk0位输入我们默认为50M,areset位复位高电平有效,c0位输出,locked位输出标志位,然后输入我们100M改为50M,下一步。

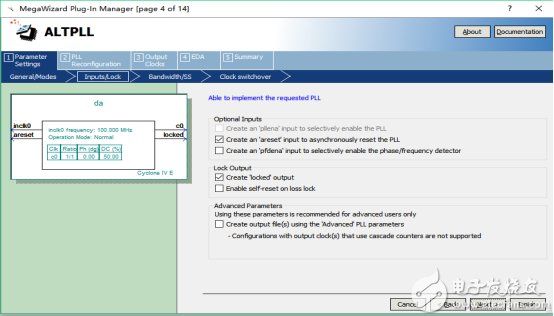

为了只观的看到各个引脚的情况,我们下一步,不进行操作。

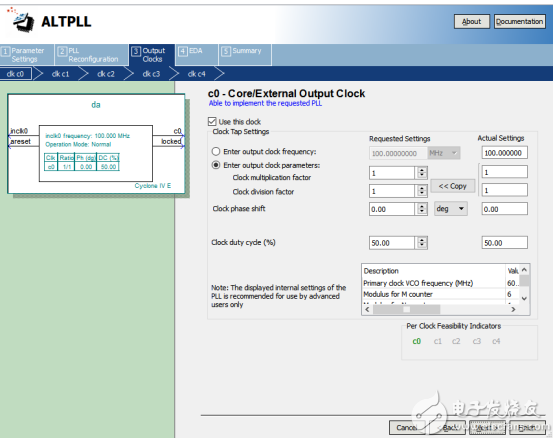

我们可以改我们的输出时钟为多少,可以改输出时钟的相位,占空比,我们写入输出位200M,占空比为50%,然后下一步。

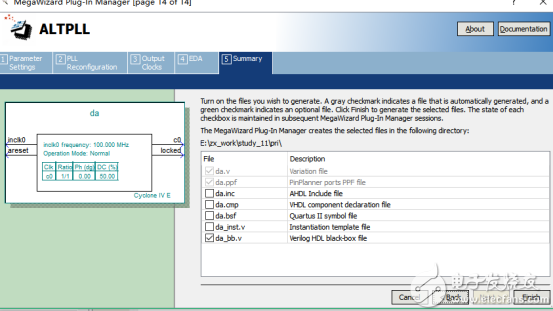

之后不停的下一步,出现下面的界面,就点击完成Finish,这样就完成了IP核的建立。

之后我们打开我们生成的IP核代码,然后例化。

设计代码:

设计模块

0modulepll(clk,clk_200M,rst_n,locked);

1inputclk;

2inputrst_n;

3

4outputclk_200M;

5outputlocked;

6

7

8 my_pll my_pll_inst(//例化IP核

9 .areset(~rst_n),

10 .inclk0(clk),

11 .c1(clk_200M),

12 .locked(locked)

13);

14endmodule

测试模块

0`timescale1ns/1ps

1

2modulepll_tb();

3regclk;

4regrst_n;

5

7wireclk_200M;

8wirelocked;

9initialbegin

10 clk=1'b1;

11 rst_n=1'b0;

12 #200.1rst_n=1'b1;

13

14 #2000.1$stop;

15

16 end

17

18 always#10clk=~clk;

19 pll pll_dut(

20 .clk(clk),

21 .rst_n(rst_n),

23 .clk_200M(clk_200M),

24 .locked(locked)

25 );

26endmodule

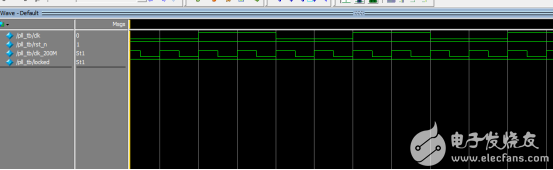

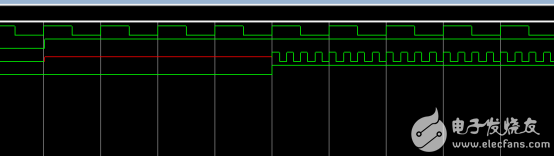

仿真图:

在仿真中我们看一看到我们生成的时钟是200M,然后我们可以用锁相环生成的标志位给用200M时钟的电路当复位,如下:

-

FPGA

+关注

关注

1630文章

21761浏览量

604410 -

锁相环

+关注

关注

35文章

588浏览量

87817

发布评论请先 登录

相关推荐

FPGA学习系列:14. 锁相环pll设计

FPGA学习系列:14. 锁相环pll设计

评论