英特尔与美光闪存研发策略联盟的分道扬镳,为闪存技术的路线之争揭开序幕。

最近的新闻报导指出,英特尔(Intel)与美光(Micron)闪存研发策略联盟的分手,肇因于对未来3D NAND Flash发展的看法差异,想来合理,且早有征兆。

NAND Flash的结构只比一般CMOS要复杂一点。CMOS结构最上层是金属闸极,最底下是源极和漏极,闸极和源极与漏极之间以氧化层相隔。NAND Flash就只在氧化层中再加入一层结构以储存电荷,以此层中电荷的有无影响CMOS电压阈值以代表储存的「0」或「1」讯号。

储存电荷的这一层材料有讲究,因而NAND Flash的制程分为两派。浮动闸极(floating gate)一派用多晶硅(polycrystalline),常用来做闸极的导电物质;电荷捕捉(charge trap)一派则用氮化硅(silicon nitride)此种绝缘体。差异在电荷能否在此层中流动与否,因此两种NAND Flash的制程和特性相差极大。

理论上电荷捕捉因为绝缘体的材质会有几个好处:制程简单、晶粒尺寸小、可靠性高、良率也高(因为它对此层与底层源、漏极之间氧化层缺陷的耐受度较高),又因为电荷于其上不会自由流动,一个电荷捕捉节点上就可以储存2个甚至3个位元。尽管理论上有这么多好处,但NAND Flash在平面制程时代的主流制程还是浮动闸极。用电子捕捉制成的产品不仅良率未能令人满意,资料写入速度更需要耐心,即使做成最低阶的micro SD卡也嫌慢,在山寨手机年代有个浑称叫「慢慢卡」。

但是到了3D NAND Flash时代事情有了中转,制程主流变成电荷捕捉,浮动闸极技术只有美光和英特尔联盟使用。一般文献上只说电荷捕捉适于垂直元件,详细的原因是3D制程在高度方向的侧面没法子做光刻,只能依物质的特性做选择性蚀刻。所以在3D制程中垂直方向的各层元件能共享的物质越多越好,制程越简单。电荷捕捉由于使用绝缘体氮化硅当电荷储存器,而电荷并不会在上下层不同元件之间流窜,所以整条上下堆叠的NAND Flash可以共享相同的一层氮化硅,而不必在每层之间(就是每个NAND Flash cell)截断,这在制程简化和良率提升上自然是利多。于是美光在未来技术路线图上开始转向电荷捕捉技术,至于英特尔则仍维持原来的浮动闸极路线,成为分手的主因。

用这个观点来检视美光前一阵子发布的64层NAND Flash产品就豁然开朗。它有两点令人惊艳,一是它的颗粒面积较小,因为它把原先安置在周边的逻辑线路全藏到存储器下方。另一个是层间距大幅缩小,相信这是美光充分利用了电荷捕捉制程的理论好处-晶粒尺寸小,而晶粒尺寸小在3D制程对应的就是层间距,因为晶粒是直摆着。层间距是未来3D制程竞争的一个重要参数,层间距小,存储器的高底比(aspect ratio)就小,深沟(trench)或孔洞(hole)的蚀刻和溅渡做的都比较轻松。

技术阵营的消长往往也牵动商业竞争。当年DRAM制程有深沟(deep trench)电容与堆叠(stack)电容两大阵营,堆叠电容的产能较多,深沟电容制程所需的制程设备就无法得到设备厂商的充分支持,现在生存的都是采用堆叠电容制程的厂商。让我们看历史会不会重演。

-

英特尔

+关注

关注

61文章

10065浏览量

172820 -

闪存

+关注

关注

16文章

1814浏览量

115288

原文标题:【名家专栏】闪存的路线之争

文章出处:【微信号:DIGITIMES,微信公众号:DIGITIMES】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

闪速存储器的闪速是指什么,闪速存储器的速度比内存快吗

一文看懂NAND、DDR、LPDDR、eMMC几种存储器的区别

什么是ROM存储器的定义

内存储器分为随机存储器和什么

铁电存储器和Flash的区别

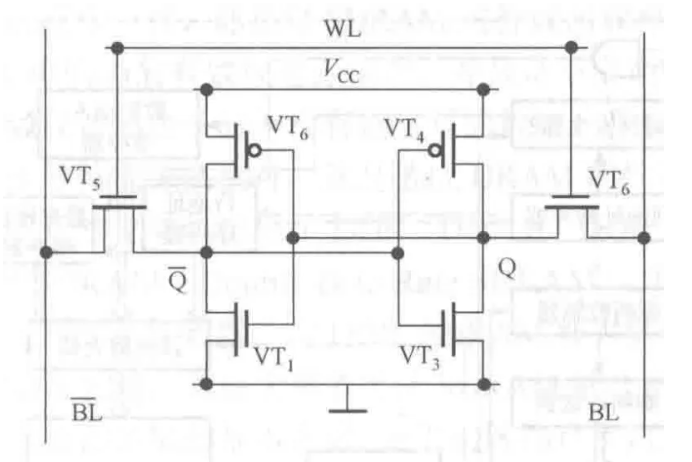

静态随机存储器的定义和工作原理

存储器芯片的内部结构及其引脚类型

高速缓冲存储器有什么作用

PLC主要使用的存储器类型

ram存储器和rom存储器的区别是什么

外部存储器是ROM还是RAM

内存储器与外存储器的主要区别

请问如何编写.bin程序使用IAR或GreenHill将文件存储到外部存储器中?

NAND存储种类和优势

快闪存储器的路线之争

快闪存储器的路线之争

评论