大家好,博主最近有事忙了几天,没有更新,今天正式回来了。那么又到了每日学习的时间了,今天咱们来聊一聊 简谈FPGA的上电复位,欢迎大家一起交流学习。

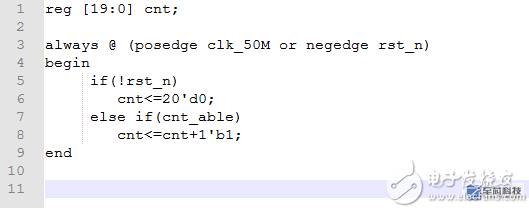

在基于verilog的FPGA设计中,我们常常可以看到以下形式的进程:

信号rst_n用来对进程中所用变量的初始化,这个复位信号是十分重要的,如果没有复位,会导致一些寄存器的初始值变得未知,如果此时FPGA就开始工作的话,极易导致错误。

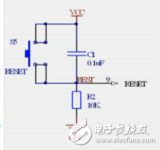

那么,这个复位信号来自何处?难道我们做好的系统,每次上电后都要手动按一下reset按钮么?

答案是否定的!这个复位信号其实是由特定的程序来产生的,系统每次上电,都会由该程序产生一个复位信号,从而避免了手动复位。

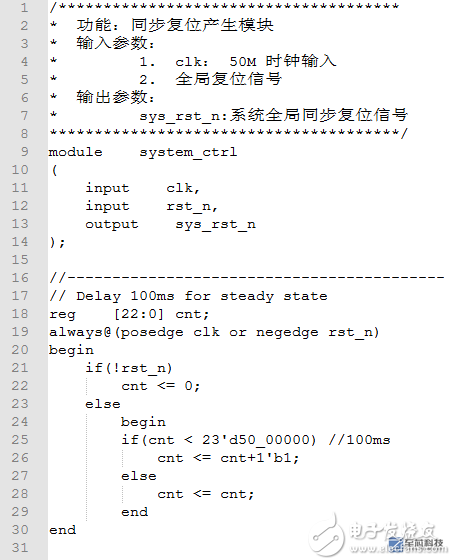

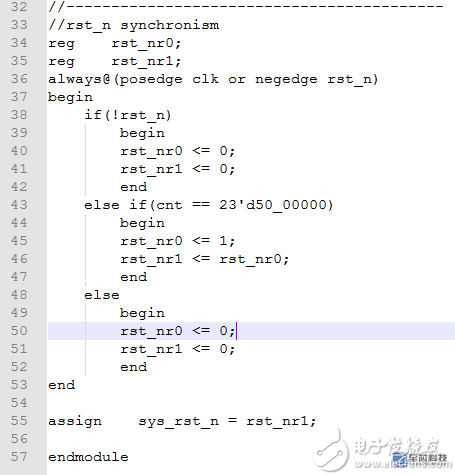

在网上找了多种方案,觉得只有这个程序比较简单实用,转来如下:

说明:

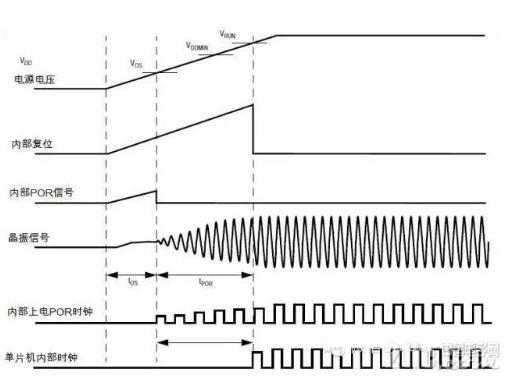

1.第一个进程用来延时,当上电后,延时100ms,以保证FPGA内部达到稳定状态;此时sys_rst_n始终为0,也就是系统时钟处于复位状态中;

2.当100ms延时结束后,sys_rst_n与系统时钟同步释放,即sys_rst_n拉高,复位结束,系统开始正常工作。

今天就聊到这里,各位,加油。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1663文章

22493浏览量

638972 -

Verilog

+关注

关注

30文章

1374浏览量

114709

发布评论请先 登录

相关推荐

热点推荐

Spartan-6 FPGA是否需要设计中的上电复位电路

您好Xilinx社区,有人能否就Spartan-6 FPGA是否需要设计中的上电复位电路给出明确的答案?在附图中,我们的设计中有这个上电复位

发表于 04-18 10:15

DSP上电复位配置什么?

1. DSP上电复位配置什么? DSP的大、小端,自启动(boot)模式,PCIe模式,网络协处理器时钟选择需要在上电复位的时候选择,怎么选择? 依靠上电时候锁定DSP Device

发表于 12-14 16:01

简谈FPGA的上电复位

发表于 04-19 10:17

上电复位和按键复位区别

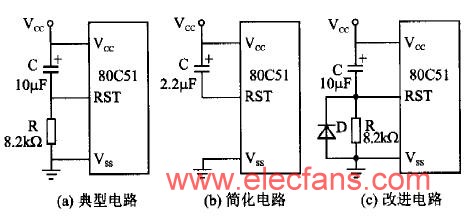

上电复位是指上电压从无到有在RESET处会先处于高电平一段时间,然后由于该点通过电阻接地,则RESET该点的电平会逐渐的改变为低电平,从而使得单片机复位口电平从1转到0,达到给单片机

发表于 10-20 15:24

•12w次阅读

上电复位信号的认识_POR和PUC的关系

POR是上电复位信号,它只在以下两个事件发生时产生:1、芯片上电。2、RST/NMI设置成复位模式,在RST/NMI引脚上出现低电平信号。

单片机上电复位与欠压复位的过程解析

上电复位:是由外部总线产生的一种异步复位,单片机电压监测电路检测到电源电压VDD上升时,会产生一个上电复位脉冲,由内部计时器进行延时后等待电

发表于 03-23 15:14

•1.1w次阅读

单片机基础入门:什么是上电复位,复位电路怎么设计

什么是单片机的上电复位众所周知,单片机属于数字电路,数字电路里只有0(低电平)和1(高电平)之分,单片机要么是高电平复位,要么是低电平复位。以5V单片机为例,

发表于 11-05 13:06

•13次下载

FPGA复位电路的实现——以cycloneIII系列芯片为例

有人说FPGA不需要上电复位电路,因为内部自带上电复位信号。也有人说FPGA最好加一个上

单片机上位复位电路与按键与上电复位的区别

单片机上位复位电路与按键与上电复位的区别 单片机的复位电路常用于保证单片机在复位状态下正常工作,以便单片机能够在正确的起始状态下启动。常见

简谈FPGA的上电复位

简谈FPGA的上电复位

评论