设计背景:

我们从开始学习FPGA。到现在也慢慢的学到了血多的东西,那么我们就应该慢慢的去学习深一点的东西,我就给大家分享一个自动售货机的简单历程,帮助大家理解和学习我们的FPGA,为以后的学习做一个铺垫。

设计原理:

设计要求:一听饮料需要2.5美元,规定只能投入一美元,0.5美元的硬币

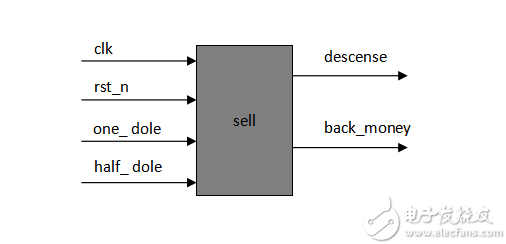

设计架构图:

设计代码:

设计模块

0modulesell(clk,rst_n,one_dole,half_dole,des

1 inputclk;

2 inputrst_n;

3 inputone_dole; //输入1美元

4 inputhalf_dole; //输入0.5美元

5

6 outputregdescense; //是否买到的标志

7 outputreg[2:0]back_money;//找回的钱

8

9 parameters0 =2'b00,s1 =2'b01,s2 =2'b10

10

11 reg[1:0]state;

12 reg[4:0]money;

13

14 reg[1:0]state_x;

//状态机两段式表示

15 always@(posedgeclk ornegedgerst_n)

16 if(!rst_n)

17 begin

18 state_x <=s0;

19 end

20 else

21 begin

22 state_x <=state;

23 end

24

25 always@(posedgeclk ornegedgerst_n)

26 if(!rst_n)

27 begin

28 money <=5'b0;

29 state <=s0;

30 end

31 else

32 begin

33 case(state)

34 s0:begin

35 //判断投入的钱是多少

36 if(one_dole)

37 begin

38 money <=money

39 state <=s1;

40 end

41 elseif(half_dole)

42 begin

43 money <=money

44 state <=s1;

45 end

46 else

47 begin

48 state <=s0;

49 money <=money

50 end

51 end

52 //判断和商品的价格是否一样

53 s1:begin

54 if(money <25)

55 begin

56 state <=s0;

57 end

58 else

59 begin

60 state <=s0;

61 money <=5'b0;

62 end

63 end

64 endcase

65 end

66

67 reg[1:0]state_s;

68 always@(posedgeclk ornegedgerst_n )

69 if(!rst_n)

70 begin

71 descense <=1'b0;

72 back_money <=3'b0;

73 state_s <=s0;

74 end

75 else

76 begin

77 case(state_s)

78 s0:begin

79 if(money <25)

80 begin

81 back_money <=

82 descense <=1'

83 end

84 else

85 //找回的钱和买到的标志

86 begin

87 back_money <=

88 descense <=1'

89 state_s <=s1;

90 end

91 end

92 s1:begin

93 descense <=1'b0;

94 state_s <=s0;

95 end

96 endcase

97 end

98endmodule

测试模块

0`timescale1ns/1ps //时间精度

1

2modulesell_tb();

3

4 //定义我们的端口

5 regclk;

6 regrst_n;

7 regone_dole;

8 reghalf_dole;

9

10 wiredescense;

11 wire[2:0]back_money;

12

13 initialbegin

14 clk =1'b1;

15 rst_n =1'b0;

16 one_dole =1'b0;

17 half_dole =1'b0;

18 #200.1rst_n =1'b1;

19

20 //模拟蔬输入的钱数

21

22 #200 one_dole =1'b1;

23 #20 one_dole =1'b0;

24

25 #200 one_dole =1'b1;

26 #20 one_dole =1'b0;

27

28 #200 one_dole =1'b1;

29 #20 one_dole =1'b0;

30

31 #1000.1

32 #200 half_dole =1'b1;

33 #20 half_dole =1'b0;

34

35 #200 one_dole =1'b1;

36 #20 one_dole =1'b0;

37

38 #200 one_dole =1'b1;

39 #20 one_dole =1'b0;

40

41 #1000$stop; //停止仿真

42 end

43

44 always#10clk =~clk;

45

46 sell sell_dut( //例化端口

47 .clk(clk),

48 .rst_n(rst_n),

49 .one_dole(one_dole),

50 .half_dole(half_dole),

51 .descense(descense),

52 .back_money(back_money)

53 );

54endmodule

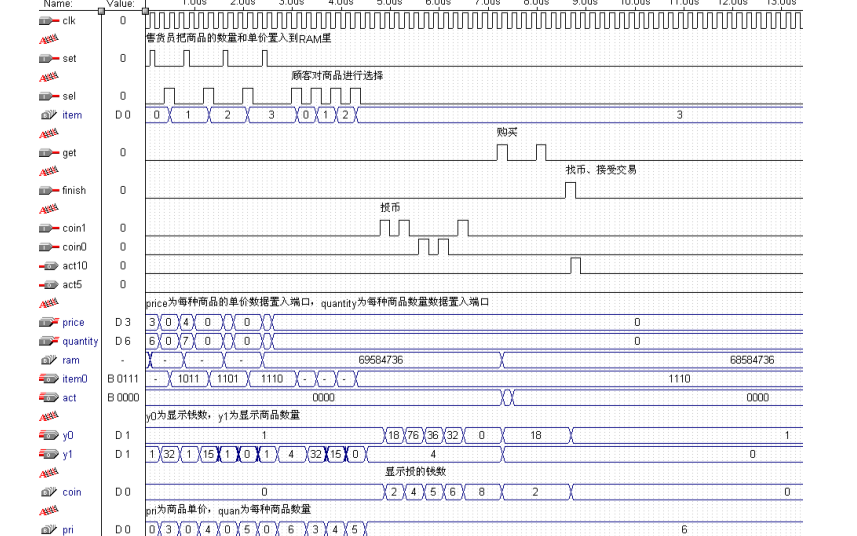

仿真图:

我们从仿真中可以看到当我们的钱数投够的时候,就给一个买到的标志位,如果投的超过商品的价格,那么我们就给一个买的标志位,然后找回我们投的多的钱。

-

FPGA

+关注

关注

1629文章

21750浏览量

604081

发布评论请先 登录

相关推荐

【FPGA设计实例】自动售货机VHDL程序与仿真

至芯昭哥带你学FPGA之_100天之旅_自动售货机设计

4G无线工业路由器自动售货机的应用

嵌入式自动售货机能实现什么功能?

基于FPGA的自动售货机主控制系统的设计

基于VHDL的自动售货机控制模块FPGA实现

自动售货机方案/设计/开发/项目

FPGA学习系列:21. 自动售货机的设计

FPGA学习系列:21. 自动售货机的设计

评论