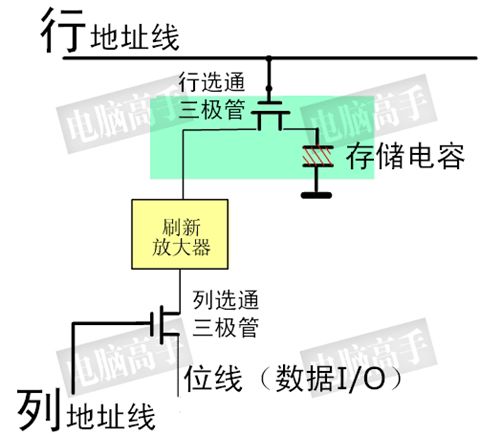

存储原理

存储原理示意图:行选与列选信号将使存储电容与外界间的传输电路导通,从而可进行放电(读取)与充电(写入)。另外,图中刷新放大器的设计并不固定,目前这一功能被并入读出放大器(Sense Amplifier ,简称S-AMP);

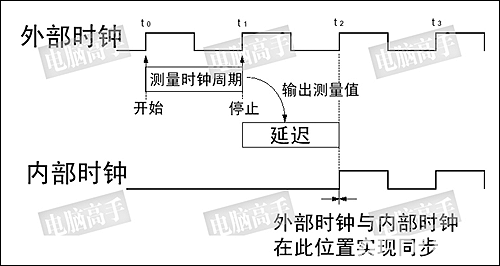

DLL

延迟锁定回路(DLL)的任务是根据外部时钟动态修正内部时钟的延迟来实现与外部时钟的同步;

DLL有时钟频率测量法(CFM,Clock Frequency Measurement)和时钟比较法(CC,Clock Comparator); CFM是测量外部时钟的频率周期,然后以此周期为延迟值控制内部时钟,这样内外时钟正好就相差一个时钟周期,从而实现同步。DLL就这样反复测量反复控制延迟值,使内部时钟与外部时钟保持同步。

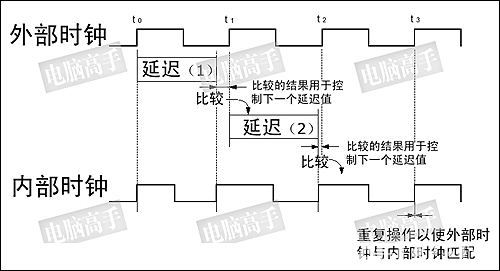

CC的方法则是比较内外部时钟的长短,如果内部时钟周期短了,就将所少的延迟加到下一个内部时钟周期,然后再与外部时钟做比较,若是内部时钟周期长了,就将多出的延迟从下一个内部时钟刨除,如此往复,最终使内外时钟同步。

CFM式DLL工作图

CC式DLL工作图

CFM与CC各有优缺点,CFM的校正速度快,仅用两个时钟周期,但容易受到噪音干扰,如果测量失误,则内部的延迟就永远错下去。CC的优点则是更稳定可靠,如果比较失败,延迟受影响的只是一个数据,不会涉及到后面的延迟修正,但它的修正时间要比CFM长。

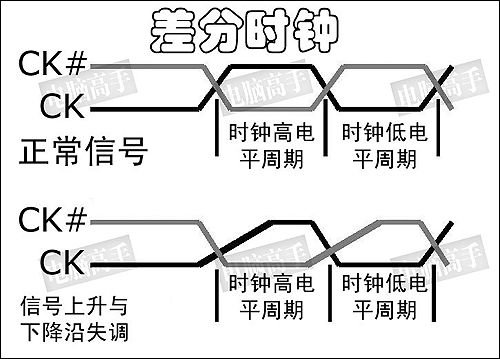

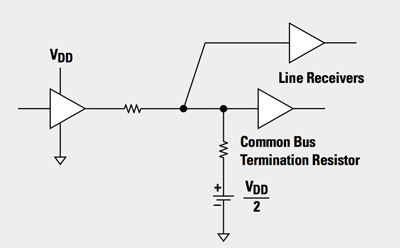

CK#起到触发时钟校准的作用,由于数据是在CK的上下沿触发,造成传输周期缩短了一半,因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求CK的上下沿间距要有精确的控制。但因为温度、电阻性能的改变等原因,CK上下沿间距可能发生变化,此时预期相反的CK#就起到纠正的作用(CK上升快下降慢,CK#则是上升慢下降快)。

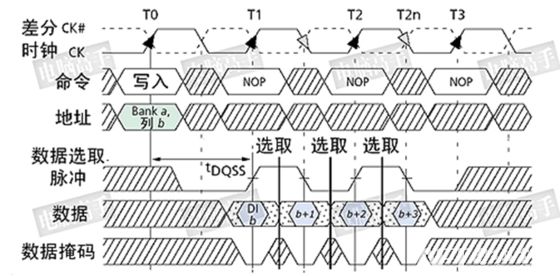

在写入时,以DQS的高/低电平期中部为数据周期分割点,而不是上/下沿,但数据的接收触发仍为DQS的上/下沿,DQS是双向信号,读内存时,由内存产生DQS的沿和数据的沿对齐,写入内存时,由外部产生,DQS的中间对应数据的沿,即此时DQS的沿对应数据最稳定的中间时刻;

图形解析

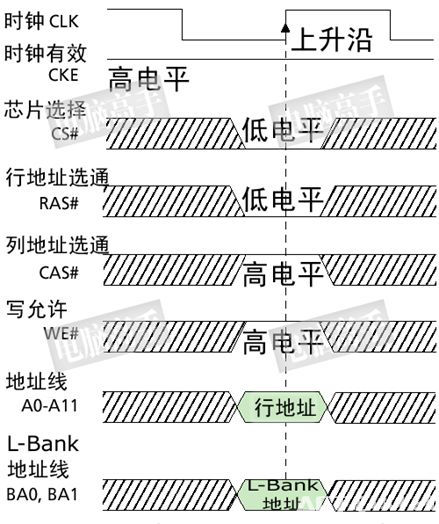

读写操作示意图,读取命令与列地址一块发出(当WE#为低电平是即为写命令)

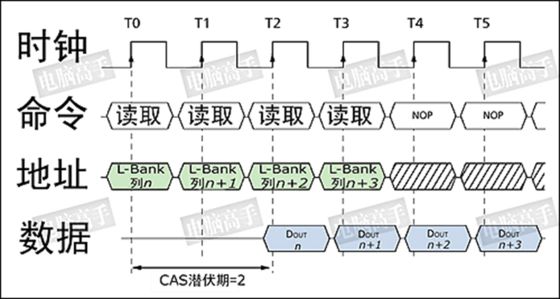

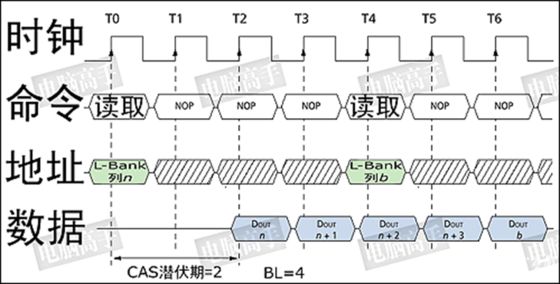

非突发连续读取模式:不采用突发传输而是依次单独寻址,此时可等效于BL=1,虽然可以让数据是连续的传输,但每次都要发送列地址与命令信息,控制资源占用极大。

突发连续读取模式:只要指定起始列地址与突发长度,寻址与数据的读取自动进行,而只要控制好两段突发读取命令的间隔周期(与BL相同)即可做到连续的突发传输。

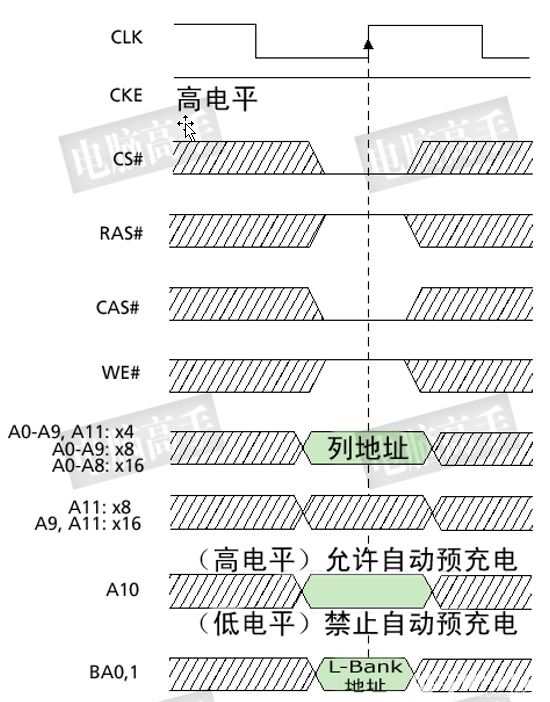

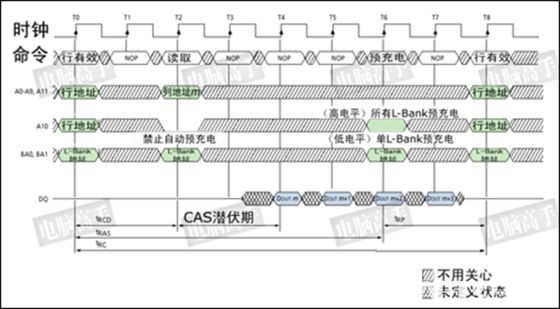

读取时预充电时序图:图中设定:CL=2、BL=4、tRP=2。自动预充电时的开始时间与此图一样,只是没有了单独的预充电命令,并在发出读取命令时,A10地址线要设为高电平(允许自动预充电)。可见控制好预充电启动时间很重要,它可以在读取操作结束后立刻进入新行的寻址,保证运行效率。

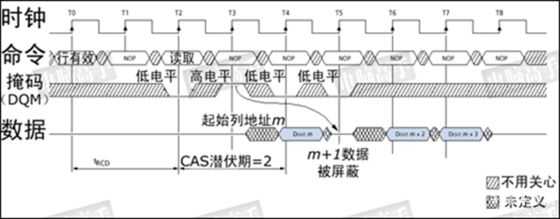

读取时数据掩码操作,DQM在两个周期后生效,突发周期的第二笔数据被取消

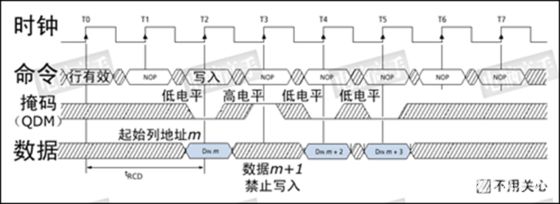

写入时数据掩码操作,DQM立即生效,突发周期的第二笔数据被取消

-

放大器

+关注

关注

143文章

13584浏览量

213368 -

DDR

+关注

关注

11文章

712浏览量

65318

原文标题:【博文连载】DDR扫盲——DDR的特性分析

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于DDR3存储器的数据处理应用

检验DDR, DDR2 和DDR3 SDRAM命令和协议

DDR存储器电气特性验证

基于FPGA的DDR2 SDRAM存储器用户接口设计

基于FPGA的DDR3多端口读写存储管理的设计与实现

DDR的特性分析与存储原理

DDR的特性分析与存储原理

评论