6月24日-27日,全球芯片设计及半导体知识产权(IP)领域内最负盛名的“设计自动化大会(DAC)”将在旧金山举行,每年的DAC都吸引了来自全球的EDA工具厂商、IP厂商和芯片设计师参加。作为该项活动的第55届,组委会公布本届大会为一些新的技术扩展了展览面积并新增了研讨话题,包括人工智能与机器学习、汽车和物联网等等。但是值得大家关注的还有一个新的领域:RISC-V开源硬件。

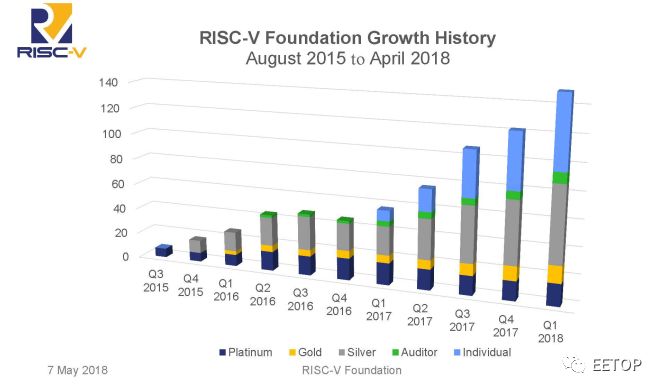

谷歌、高通、三星、华为、特斯拉……随着越来越多的行业巨头加入RISC-V基金会(RISC-V Foundation),RISC-V架构的行业认可度快速提升,基于该架构的新兴产品和解决方案开始在市场中不断涌现。而RISC-V社群在第55届DAC大会上的表现将会再次引起行业的高度关注,此次RISC-V基金会将与其成员公司 Imperas Software、Microsemi、SiFive、Syntacore,UltraSoC及Western Digital 在2638号展位上向芯片设计行业介绍其最新的技术与生态建设进展。

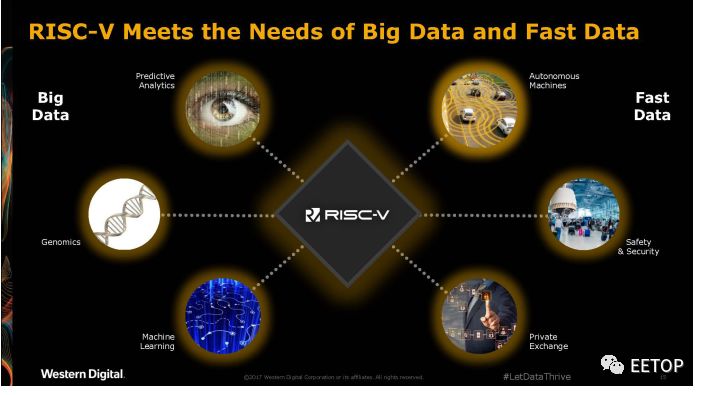

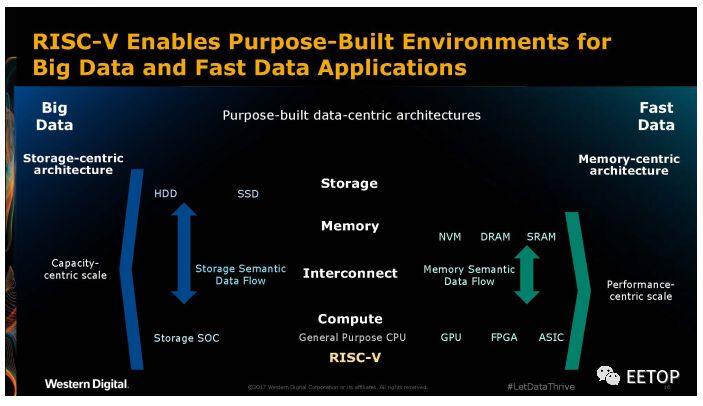

北京华兴万邦管理咨询有限公司首席分析师刘朝晖表示:“RISC-V生态在第55届DAC定会引起广泛的关注,这是因为RISC-V开源硬件的价值已经不再仅仅是节省NRE和授权费用了,一些领先的芯片设计公司开始利用RISC-V ISA指令架构定义和实现自己的芯片特性,已在市场中形成独有的差异化优势。这是Microsemi和Western Digital等公司已经用实际产品证明过的一条创新之道。”

在此次DAC大会前,RISC-V社群中的许多成员已经在不断为行业带来新的亮点和热点。UltraSoC和Imperas于6月21日联合宣布:双方将达成一项广泛的合作,为多核系统级芯片(SoC)开发人员提供结合了嵌入式分析技术和虚拟平台技术的强大组合。根据协议条款,UltraSoC将把Imperas开发环境的关键元素纳入其提供的工具中,从而为设计人员提供一个统一的系统级预处理和后处理芯片开发流程,显著地缩减了产品开发时间和整体开发成本。

通过结合半导体知识产权(IP)和相关软件,UltraSoC提供行业领先的独立片上监测、分析和调试技术。Imperas首创的虚拟平台方法使得软件开发人员能尽早启动SoC项目的相关开发工作,并提供一系列调试工具为开发人员提供系统全局视角。将两家公司提供的技术结合起来可创造一个强大的、带有一个通用软件调试环境的集成化设计流程,为项目发展提供平稳过度。

北京华兴万邦管理咨询有限公司高级分析师陈皓表示:“就在刚刚过去的这个五月,RISC-V生态在全球多地迎来了一次集中式的爆发,多项行业活动在世界不同地方如火如荼开展,并得到了行业内外的广泛关注,蓬勃发展前景一览无余。无论RISC-V生态最终走向何方,2018年的5月是芯片设计领域内值得记住的一个月份。”

让我们先将目光聚焦至西班牙巴塞罗那。5月7-10日,第8届RISC-V研讨会在巴塞罗那举行,谷歌、IBM、英伟达、恩智浦、西部数据、UltraSoC、SiFive、Microsemi等一众RISC-V领域的翘楚企业参加会议。该会议吸引了数百名与会者,从大企业、初创企业到学术机构和普通爱好者,皆踊跃参加。

UltraSoC作为目前唯一一家提供RISC-V跟踪解决方案的公司以及本次活动的赞助商,其首席执行官Rupert Baines携首席技术官、销售和工程代表等6名成员参与活动。会议期间,UltraSoC首席技术官Gajinder Panesar发表了主题演讲,对UltraSoC领导的RISC-V规范调试工作组(Debug Working Group)及UltraSoC的跟踪解决方案进行了介绍。此外,UltraSoC还在其展位上演示了基于SiFive和Andes内核的运行控制和指令跟踪案例,吸引大量观众驻足交流和观看。

UltraSoC的RISC-V处理器跟踪解决方案从今年2月开始已经全面供货,这是业界首款商用RISC-V处理器跟踪IP产品,也是RISC-V生态系统中关键的推动性技术。除了作为一种独立的IP模块来集成至UltraSoC的SoC架构中,UltraSoC还提供各种不同的打包选择项来使RISC-V设计人员快速上手并实现运转,而无须将UltraSoC用于其他功能。

处理器跟踪功能支持对程序的行为进行详细的、逐条指令式的查看,它于系统开发人员而言是一项关键需求。UltraSoC的RISC-V跟踪编码器同时支持32位和64位RISC-V设计,IP模块可以顺利地与UltraSoC产品组合的其他部分进行集成;其所有产品均采用支持开放架构和业界标准架构方式,在SoC的核心部分设置自分析功能。

看过巴塞罗那的行业盛景,让我们再将视线转移至中国上海。5月15日,世界领先的商业RISC-V处理器IP提供商SiFive在上海举办首届(2018)技术研讨会,来自SiFive、西部数据、Microsemi、灿芯半导体、UltraSoC及中科院计算所在内的专家学者、行业精英齐聚一堂,共同对RISC-V技术发展趋势、生态系统、应用及原型芯片的快速定制展开深入探讨。该研讨会的举办,正值全球半导体产业联盟董事会在中国举办,UltraSoC首席执行官Rupert Baines及其中国团队参加了该次研讨会。

UltraSoC作为RISC-V生态系统的积极参与者,早在去年9月就与SiFive形成了良好的合作关系。UltraSoC的嵌入式分析半导体知识产权(IP)通过SiFive DesignShare生态系统对外提供,该生态系统为任何公司、发明人和创客都提供了驾驭客制化芯片动力的能力。UltraSoC的调试与追踪功能可以支持SiFive Freedom平台的用户去广泛对接其设计中所用到的各种工具与接口。

“UltraSoC致力于提升新的芯片设计的数量,而我们与SiFive在DesignShare生态中的合作是这项工作的自然延伸。”UltraSoC首席执行官Rupert Baines表示。“我们专注于推动半导体行业新兴力量的加速形成,所采用的方法既包括在RISC-V基金会中发挥会员作用,也包括与SiFive这样的单个合作伙伴关系。通过DesignShare模式来提供UltraSoC的IP,将使各地的芯片开发商都能够尽享开源硬件的优点,并为市场带来全新的、创新的设计。”

领先厂商两岸三市造势,64位RISC-V立志高端。在SiFive举办技术研讨会的同期,另一家为RISC-V生态系统做出积极贡献的厂商晶心科技(Andes Technology)也于5月3日、15日、17日分别在新竹、深圳、上海三地举办第十三届晶心嵌入式技术论坛。该论坛以“万物联网划世代‧智能生活跃云端”为主题,聚焦于晶心科技新一代微处理器指令集架构AndeStar V5,以及AI结合IoT而成的AIoT领域重点应用。UltraSoC作为晶心科技的合作伙伴,其首席执行官Rupert Baines也受邀参与了本次活动。

UltraSoC先进的嵌入式分析技术目前已获晶心科技采用,来支持其AndesCore系列RISC-V处理器。利用UltraSoC包括业界唯一商用RISC-V处理器跟踪解决方案在内的独一无二的IP产品系列,晶心科技可以实现其复杂应用嵌入式产品的开发加速和调试增强,这些应用包括人工智能(AI)、计算机视觉、网络控制器和存储等。

晶心科技的内核都基于高性能的AndeStar V5 32位及64位架构,与UltraSoC的合作伙伴关系将使客户在使用Andes V5 N25及NX25处理器时,可以选择并集成先进的嵌入式分析功能。使用晶心科技高性能32位及64位处理器内核的客户,在RISC-V处理器追踪功能之外,还能够利用UltraSoC的SoC分析与调试IP,这些功能结合在一起就给SoC设计师带来了全面的可视性,不仅可以观察内核的性能,而且还可以观察整个系统的运行。

除了SiFive和晶心科技,UltraSoC的解决方案还获得了Codasip、Microsemi、Roa Logic、Syntacore和Esperanto等主要RISC-V处理器供应商和多家工具供应商的支持和采用。UltraSoC正在携手这些厂商共同推动RISC-V的生态向更广阔的空间发展。

北京华兴万邦管理咨询有限公司高级分析师胡霞表示:“今年年初以来,我们一直在对国内外媒体上的RISC-V相关话题进行监测,结果是国内媒体对RISC-V的报道数量相比2017年有巨大的增加。尽管产业化的道路还很漫长,但是国内芯片设计企业的确可以考虑利用指令架构的创新来走出新路。”

也许,加州大学伯克利分校最初开发RISC-V处理器架构时并不会想到该架构会发展得如此迅速甚至火爆,然而事实就在眼前,随着一场“RISC-V的红色五月盛宴”以及在第55届DAC上RISC-V生态的宏大亮相,产业发展的新机遇正在形成。正如UltraSoC的首席执行官Rupert Baines所言:“RISC-V,2018大势所向。”

-

芯片

+关注

关注

455文章

50846浏览量

423847 -

机器学习

+关注

关注

66文章

8419浏览量

132678 -

RISC-V

+关注

关注

45文章

2283浏览量

46177

原文标题:RISC-V能否再度掀起热浪?

文章出处:【微信号:eetop-1,微信公众号:EETOP】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

《RISC-V能否复制Linux 的成功?》

risc-v芯片在电机领域的应用展望

学习RISC-V入门 基于RISC-V架构的开源处理器及SoC研究

每日推荐 | 通用电源项目分享,RISC-V开源硬件分享会

【直播资料】开源芯片系列讲座第07期:基于RISC-V的Linux发行版及软件生态

【转载】RISC-V 能打 50 年!risc-v 现在和未来的发展

开源硬件RISC-V的目标是颠覆处理器行业

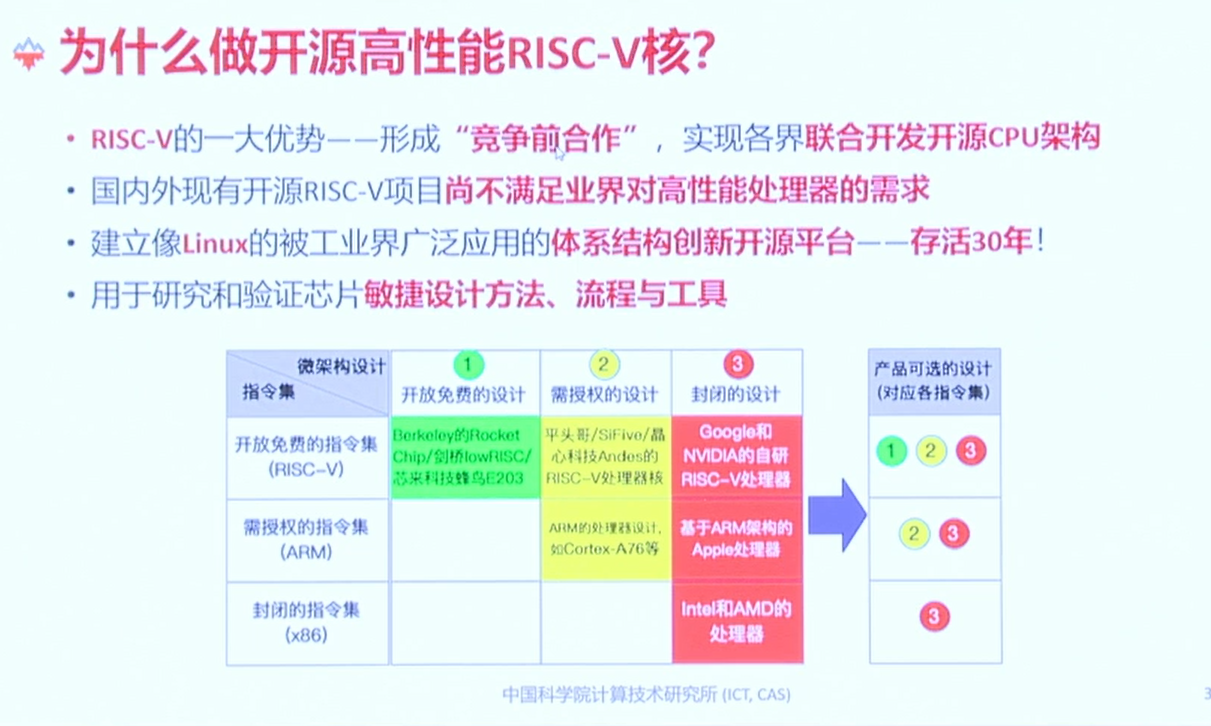

为什么做开源高性能RISC-v核,香山开源高性能RISC-V处理器开发流程

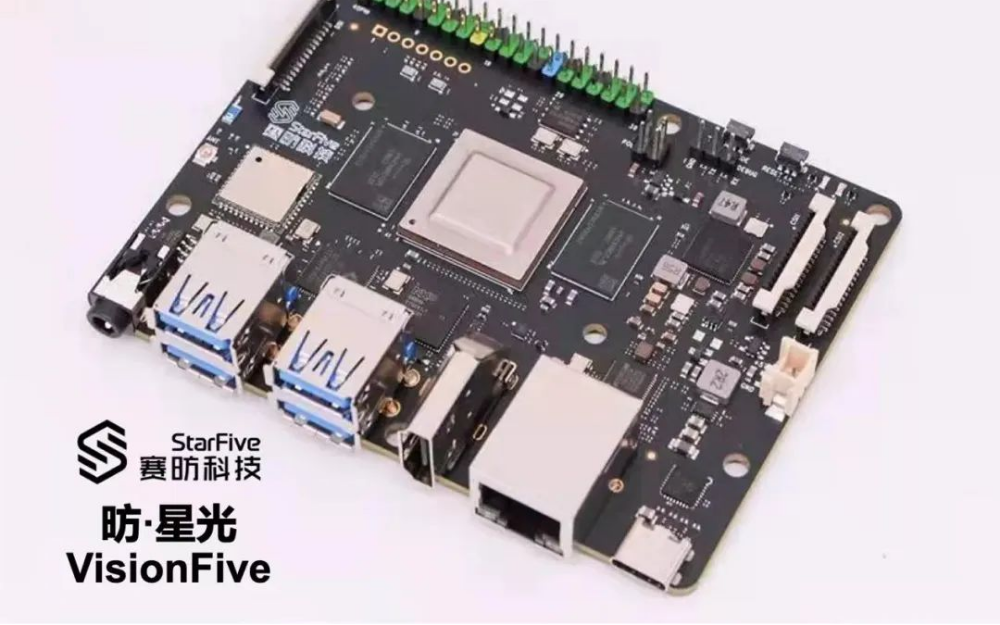

欧拉开源操作系统成功适配VisionFive RISC-V单板计算机

一个新的领域:RISC-V开源硬件

一个新的领域:RISC-V开源硬件

评论