介绍

在多个大趋势的推动下,推动世界对半导体需求的技术繁荣依然强劲。无线基础设施、物联网、人工智能、数据中心和电动汽车是推动对先进半导体 IC 需求增加的应用示例。随着每个单独的 IC 中包含更多功能,测试要求也会增加,降低成本变得更具挑战性。半导体制造商如何提高其最终产品的复杂性,同时降低测试成本?

测试系统未标准化

从广义上讲,半导体开发过程包括设计、制造和测试。今天,IC 设计人员使用 EDA(电子设计自动化)软件工具。这些工具是标准化的,大大简化了设计过程。晶圆的制造设备在一定程度上也是标准化的,因为许多工艺和设备是代代相传的。ATE 系统不能这样说。缺乏标准和 IC 复杂性的增加导致测试成本上升。研究表明,封装和测试占产品总成本的 50% 到 70% 之间。

降低测试成本

降低测试成本的一个明显方法是采用更高的并行度并同时测试多个部分。每当 ATE 系统并行测试更多部件时,吞吐量就会提高。例如,如果之前的测试平台可以并行测试四个设备,总测试时间为 10 秒,那么每个设备测试是 2.5 秒。使用每秒 0.02 美元的假设成本,那么每个设备都有 0.05 美元的测试成本。通过将 ATE 系统升级到八进制站点甚至 16 个站点的测试仪,测试成本显着下降,分别为 0.025 美元和 0.0125 美元。与 16 个站点的测试设置相比,这项 75% 的测试成本节省比原始测试成本节省了 0.0375 美元。

接下来,想象一下总测试时间是否可以减少一半。由于 ATE 生产车间测试工程师将最大限度地利用资源来测试器件,因此减少测试时间的方法是提高驱动信号到被测器件 (DUT) 和比较器信号返回到 FPGA 的速度。驱动器和比较器 IC 所在的引脚电子速度提高了 2 倍,将测试时间缩短了一半。计算测试成本的数学与前面的示例一样简单。测试 16 台设备需要 5 秒,而不是 10 秒。这意味着每台设备的测试成本为 0.00625 美元,是 0.0125 美元的一半。虽然实际测试时间各不相同,但这个假设示例清楚地展示了更快系统和更高密度卡的潜在节省。

更高的密度和速度

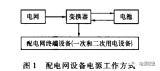

前面提到的引脚电子驱动板具有驱动器和比较器 IC。图 1中的 ATE 框图显示了MAX32007所在的位置(DCL + DAC + SWITCHES 盒)。MAX32007 是 ADI 最新发布的 8 通道 3Gbps 引脚驱动器。

图 1. 通用 ATE 系统框图。

高密度、八通道、高速 3Gbps MAX32007 具有集成的 14 位电平设置 DAC、电缆下垂补偿和压摆率控制,可优化 DUT 的波形。

电缆下垂补偿

由于 PCB 上的长迹线和/或长或有损耗的同轴电缆,驱动到 DUT 的波形和返回信号可能会衰减或退化。当波形受到这种影响时,有效数据速率会降低,或者更糟的是,数据无法使用,从而影响测试的吞吐量和成本。MAX32007 在输出波形中加入了长 (CDRPL) 和短 (CDRPS) 双时间常数,通过受控量的过冲和下冲来恢复圆润边沿。

图 2. 驱动器电缆下垂补偿的概念表示。

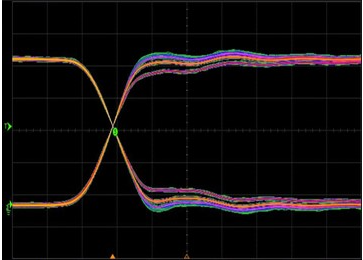

补偿量可以通过一个 3 位内部寄存器从 0 到 10% 进行编程。图 3中的示波器显示了电缆下垂补偿如何帮助信号保真度克服 24 英寸 50Ω 同轴电缆上的劣化波形的示例。外部绿色迹线表示应用到波形的 10% 补偿,内部迹线显示 0% 补偿。

图 3. 电缆下垂补偿的范围拍摄。

结论

随着半导体 IC 不断跟上最新的技术需求,测试它们所需的自动化测试设备也必须如此。Pin 电子驱动器在处理这种技术激增方面发挥着关键作用,更高密度和更高数据速率可实现下一代设备的高吞吐量和更低的测试成本。

审核编辑:郭婷

-

FPGA

+关注

关注

1664文章

22504浏览量

639300 -

驱动器

+关注

关注

54文章

9116浏览量

156515 -

半导体

+关注

关注

339文章

31248浏览量

266595

发布评论请先 登录

Siemens 工业电缆与线束在自动化系统中的技术与选型指南

当电子制造遇上光纤魔法:耐达讯自动化PROFIBUS光纤转换器如何让伺服驱动器‘起死回生’?”

耐达讯自动化Profibus 集线器如何让驱动器脱胎换骨?答案在此!

EtherCAT与Profinet协议转换在工业自动化中的应用:以汇川伺服驱动器为例

Pin电子驱动器在自动化测试设备中应用分析

Pin电子驱动器在自动化测试设备中应用分析

评论