0 引言

随着社会信息化程度的不断提高,人们对视频处理的要求越来越高,视频处理系统处理的数据量也越来越大。在嵌入式视频处理系统中,目前主流的方案主要有3种:基于ARM、基于DSP和基于FPGA。其中FPGA不同于其他两种芯片,它是一种半定制电路,拥有大量逻辑单元,通过配置这些逻辑单元,可以构建相应的电路以实现所需的功能。正因为其具有基于硬件加速的特点,FPGA被广泛应用于高速视频处理系统。对于这类视频处理系统,构建可编程片上系统(System-on-a-Programmable-Chip,SOPC)是目前的主流方案。SOPC是一种片上系统,即在一块芯片上实现整个系统的逻辑功能[1],且具有设计便捷、配置灵活、可在线调试、系统可复用等特点。在视频处理系统的接口中,HDMI是最新的高清晰度多媒体接口[2],具有高带宽、小体积、高智能、内容保护等优点,被广泛应用于高清显示器、高清电视之中[3]。

针对基于SOPC的视频处理系统,本文提出一种基于FPGA的HDMI多模式显示模块设计方法,可为SOPC提供一种通用的HDMI多模式显示组件,并可适用于多种HDMI发送器以及不同参数的视频。通过该模块,可以实现多路视频的显示,并可配置每路视频的位置与透明度,为视频处理系统实现多模式的显示提供了解决方案。

1 总体方案设计

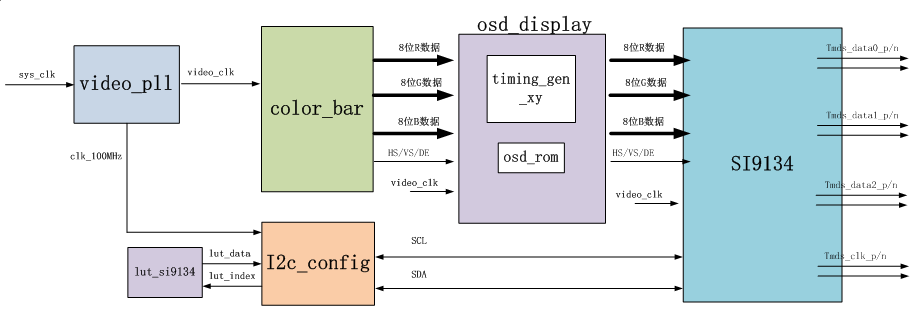

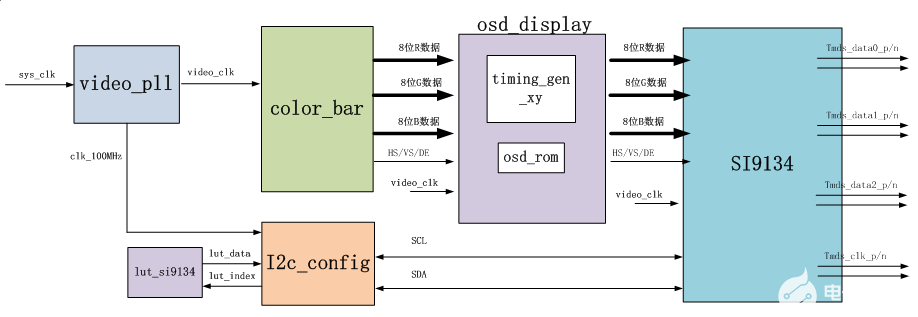

为了驱动HDMI发送芯片,以及通过ALPHA混合实现多模式显示,需要根据HDMI的工作时序设计相应的驱动电路,而且还需根据指定的坐标信息与透明度参数,对各通道视频的数据进行多级ALPHA混合计算,最后将驱动信号以及视频数据输出。根据以上功能需求,将整个模块分为两个分模块,即HDMI驱动模块和ALPHA混合模块。系统框图如图1所示。

在HDMI驱动模块中,根据HDMI接口的工作时序,设计两个计数器分别对时钟信号与行进行计数,在相应的时钟周期生成行同步信号、场同步信号和数据总线使能信号[4]。设计一个坐标指示电路,通过两个计数器对当前输出的有效视频数据的行和列进行计数,并输出计数值,此计数值用于在相应坐标读取视频数据与ALPHA混合计算。

例化4个ALPHA混合模块(数量可根据需求设定),最多可以使4路视频进行多模式显示。在ALPHA混合模块中,根据坐标指示电路生成的计数值,在指定的坐标区域发出数据读取信号对缓存的视频数据进行读取,并且在指定的区域生成相应alpha值(透明度)。设计一个ALPHA混合计算电路,其负责对前景视频数据与后景视频数据进行ALPHA混合。ALPHA混合计算电路采用流水线设计方法,将整个计算过程分为多级进行ALPHA混合计算,每一级在一个时钟周期内的计算结果保存在寄存器中,提供给下一级在下个时钟周期进行计算。ALPHA混合计算会导致数据输出延迟,因此再次例化一个坐标指示电路,将同步信号、场同步信号和数据总线使能信号都延迟相应周期后输入该电路,以产生新的同步的行和列的计数值供下一级的ALPHA混合模块使用。本实例提供4通道分割显示与PIP(双通道的画中画)显示两种显示模式用于验证。当配置的显示模式为4通道分割显示时,第一通道视频作为前景首先和预设的底色背景进行ALPHA混合,其中重叠部分背景的透明度为0(完全不显示),前景的透明度为1(完全显示),再将混合后的视频数据作为背景与第二通道的视频进行ALPHA混合,按此方案依次完成4个通道的ALPHA混合,每个通道的位置互不重叠。而进行PIP显示时第一通道的视频作为背景,第二通道的视频作为前景显示在显示器中心位置,重叠部分背景的透明度为0,前景的透明度为1。

2 HDMI驱动模块设计

HDMI驱动模块主要负责根据不同的配置信息输出相应的驱动信号,使视频数据能够通过HDMI发送器正常输出。

2.1 HDMI发送器工作方式

视频数据通过HDMI进行传输时,HDMI接收/发送芯片通过最小化传输差分信号(TMDS)的编码技术将其编码为数据包,虽然FPGA支持多种标准LVDS(低电压差分信号),但其不能完全兼容TMDS(过渡调制差分信号),因此需要通过HDMI接收/发送芯片来实现HDMI接口功能。FPGA与此类HDMI芯片的传输通常通过一组并行总线实现, 包含了数据总线、IIC总线、驱动信号。其中数据总线用于传输视频数据,IIC总线用于FPGA配置HDMI发送芯片,驱动信号中的HDMI_CLK为同步时钟信号,DE_HDMI为数据总线使能信号,HSY_HDMI为行同步信号,VSY_HDMI为场同步信号。本模块正常工作需要将HDMI芯片配置为RGB输出。HDMI接口传输RGB信号的工作时序与VGA接口的工作时序类似,但无需将数字信号转换为模拟信号。DE_HDMI、HSY_HDMI、VSY_HDMI以固定的时间关系输出,HDMI_CLK则作为基准时钟与这些信号同步。

在一场的时间段,根据视频刷新频率以及分辨率的不同,处于同步段时行同步信号首先保持一定周期的高电平,之后置低电平并在间隔相应的周期后输出视频数据,这个间隙为显示后沿。视频数据输出完成后间隔相应的周期后开始下一行的传输,这个间隙为显示前沿。场同步信号的时序依然是首先保持一定周期的高电平,之后置低电平,间隔相应的行时间(传输一行数据所需的时钟周期)后输出一场中所有的行,所有行的视频数据传输完成后间隔相应的行时间后开始下一行的传输。其时序分段如图2所示。

其中VSY_HDMI的时序分段与HSY_HDMI相同。

2.2 Verilog HDL代码设计

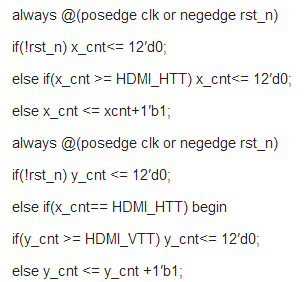

在FPGA与HDMI发送器之间,传输视频数据的方式为随同步时钟逐个传送像素数据,对于每场数据,顺序为从第一行开始从左至右传送,传送完毕后开始传送第二行,依次传送直至最后一行数据传送完毕。因此在代码中定义两个计数值,分别为x轴计数值x_cnt与y轴计数值y_cnt,x_cnt在每个时钟周期递增1,计数完一行清零;y_cnt则是x_cnt每计数完一行递增1,一场的所有行全部计数完清零。计数器Verilog HDL代码如下:

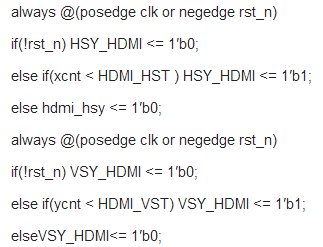

其中HDMI_HTT为传输一行所需的时钟周期的个数,HDMI_VTT为传输一场中所有行的数量。根据计数值,在相应的时间拉高行同步信号和场同步信号,其他时间置低电平,其Verilog HDL代码如下:

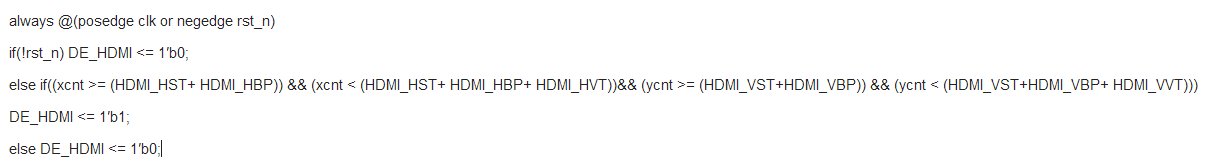

其中HDMI_HST为行同步段占用的时钟周期的个数,HDMI_VST为场同步段所有行的数量。在属于数据段的计数区域,数据总线使能信号置高电平,此时间段传送的是有效视频数据,其Verilog HDL代码如下:

其中HDMI_HBP为每行数据段占用的时钟周期的个数,HDMI_VBP为每行数据段所有行的数量。HDMI_HTT、HDMI_VTT、HDMI_HST、HDMI_VST、HDMI_HBP、HDMI_VBP等参数信号接入模块的输入端,可根据视频参数以及HDMI发送器型号输入相应的配置信息,具有较广泛的适用性。

3 ALPHA混合模块设计

本模块根据配置信息(输入的视频坐标信息、alpha值),使最多4路视频数据在指定坐标范围内显示,并按照设定的透明度进行ALPHA混合。首先将HDMI驱动模块生成的DE_HDMI、HSY_HDMI、VSY_HDMI等同步信号连接到坐标指示电路的输入端,此电路中定义两组计数器x_cnt与y_cnt,分别对输出的有效视频在显示区域内的x坐标与y坐标进行计数,从每行起始位置,在输出有效视频数据的每个时钟周期x_cnt递增1,每行有效视频数据计数完成后清零,y_cnt则从有效视频的第一行开始,在每行有效视频传输完成后递增1,场同步后清零。利用坐标指示电路生成有效视频的坐标信号,即可根据设定的视频位置信息在相应的时刻发出读请求信号,读取有效视频数据,同时在相应的时刻读取alpha值。

ALPHA混合计算电路负责将背景视频数据与前景视频数据根据当前的alpha值进行ALPHA混合。本模块通过多级流水线设计ALPHA混合计算电路,实现了ALPHA混合计算的硬件加速,极大地提升了计算速度。

对于RGB编码的视频数据,其进行ALPHA混合的公式如式1所示(该公式也适用于YUV编码的视频数据)。

其中R1、G1、B1对应混合后的视频数据的R、G、B分量,Rf、Gf、Bf对应前景数据的R、G、B分量,Rb、Gb、Bb对应背景数据的R、G、B分量。在流水线设计中,将组合逻辑分成三级,第一级对扩大后的数据通过乘法器进行乘法累加运算,第二级进行加法运算,第三级进行缩小运算,该模块框图如图3所示。

由于FPGA设计属于数字电路设计,电路层面上无法直接计算小数点。故采用将计算数据先扩大,计算完成后再缩小的方法。具体方法为先将公式左右两端分别扩大256倍,计算完成后再缩小256倍,将扩大后的公式分为三步计算。

第一步:进行乘法操作,如式(2)、式(3)所示。

第二步:进行加法操作,将第一级计算出的前景数据中间值R11、G11、B11与背景数据中间值R12、G12、B12分别相加,如式4所示。

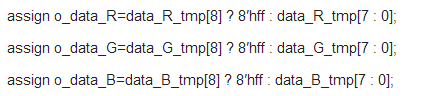

第三步:进行缩小操作,分别对第二步得到的中间值右移8位,为保证数据的精确性,对得到的数据进行溢出处理。代码如下:

其中o_data_R、o_data_G、o_data_B为完成ALPHA混合和溢出处理后的视频的R分量、G分量、B分量,data_R_tmp、data_G_tmp、data_B_tmp为完成ALPHA混合但未经溢出处理的视频的R分量、G分量、B分量。溢出处理为判断经过流水线输出的9 bit视频数据的最高位是否为0,不为0输出8′hff,否则输出前8 bit数据。

4 验证结果

将该模块作为一个基于SOPC的四通道视频处理系统的显示模块,编译后配置到FPGA中并在开发板上运行,HDMI发送器为ADV7513,加载的配置信息为4通道分割显示,并将输出的视频数据直接在显示器上显示,其实际效果如图4所示。

由于实验条件所限,只有一路信号源,因此将该信号源分别连接4个通道,可以看出每个通道的视频都能完全显示。将配置信息切换为PIP显示,重叠部分背景透明度为0,窗口为1,其实际效果如图5所示。

可以看出重叠部分窗口能完全显示,背景完全不显示。整个系统工作正常,模块实现了相应功能。

5 结论

本文设计了一个基于FPGA的HDMI多模式显示模块,该模块能够驱动HDMI输出显示多路视频,并且可以配置每路视频的显示位置以及重叠部分的透明度。通过设置驱动信息,模块可适用于多种型号HDMI的发送器以及不同参数的视频。设计中通过流水线提升了处理速度,加强了显示的即时性。因此在基于SOPC的视频处理系统中,可以作为一种通用、高速、多功能的HDMI输出显示组件,具有较好的应用前景。

-

FPGA

+关注

关注

1664文章

22502浏览量

639155 -

HDMI

+关注

关注

34文章

1916浏览量

161370 -

显示模块

+关注

关注

1文章

56浏览量

23985

发布评论请先 登录

如何用FPGA控制ADV7513实现HDMI画面显示和音频播放

u***多屏显示

例说FPGA连载29:HDMI显示驱动子板设计

例说FPGA连载89:多分辨率HDMI显示驱动设计之功能概述

例说FPGA连载90:多分辨率HDMI显示驱动设计之hdmi_controller.v模块代码解析

例说FPGA连载97:基于HDMI的AV采集显示之hdmi_controller.v模块代码解析

【FPGA DEMO】Lab 4:摄像头HDMI显示(高速--HDMI&摄像头)

带摄像机接口的HDMI输入输出FMC模块

基于FPGA的HDMI高清显示接口驱动

基于FPGA的多功能LCD显示控制器是如何实现的

【ZYNQ Ultrascale+ MPSOC FPGA教程】第十五章 HDMI字符显示实验

关于基于FPGA的HDMI多模式显示模块的设计

关于基于FPGA的HDMI多模式显示模块的设计

评论