0 引言

随着硬件技术的进步,软盘逐渐被新的存储介质代替。但部分旧设备(比如织布机等)并不支持这些更快、容量更大的存储设备,也不支持网络访问。因此,设法将存储设备虚拟成软盘,通过网络对其进行数据访问具有一定的实用价值。在台式机读写软盘过程中,数据流遵循MFM编码格式,使用CRC校验检测数据误差。

本文提出一种基于FPGA和ARM的虚拟软盘方案。在DE2-115开发平台下,将2 MB的SRAM存储器虚拟成1.44 MB软盘,通过台式机对虚拟软盘的数据进行读写,并使用树莓派实现UDP服务器,通过网络对虚拟软盘的状态和数据进行读写访问。

同时,对设计方案进行实现与验证,成功实现对虚拟软盘的镜像制作、文件读写、格式化、制作启动盘等操作,并实现局域网内设备对虚拟软盘的监控。

1 虚拟软盘核心模块的设计与实现

1.1 虚拟软盘数据分布结构

一张软盘包含80个磁道,每个磁道有2个柱面,每个柱面包含18个扇区,每个扇区包含有512 B数据。整个软盘包含有2×80×18×512 B=1.44 MB的数据量。在实际应用中,软盘通过软驱线发送到台式机的1个磁道的数据,包含数据头部、数据中部和数据尾部3个部分。

在本虚拟软盘设计中,虚拟软盘的数据分布结构示意如图1所示。

头部的长度为200 B,其中GAP数据为0x4E,用于填充磁道,共有184 B;SYNC为同步信号0x00,共有12 B;IAM表示索引信号地址标记,内容为0xC2C2C2FC,用来指示磁道开始。而数据中部则包含有18个扇区的数据,每个扇区包含地址段和数据段两部分。其中,地址段长度为72 B,数据段长度为608 B。地址段中:GAP段用于填充空间;SYNC表示同步;IDAM为地址标记;CHNR包含有磁道、磁面、扇区号、扇区内数据字节数等信息;CRC为2 B校验信息,校验起始于IDAM段,终止于CRC段。数据段中:GAP段用于填充空间;SYNC表示同步;DATAAM为地址标记;DATA包含512 B数据信息;CRC为2 B的校验信息,校验起始于DATAAM段,终止于CRC段。磁道尾部包含的数据是用于填充用的GAP段,其内容为0x4E,长度为60 B。

1.2并行CRC运算模块的原理和实现

循环冗余校验(Cyclic Redundancy Check,CRC)算法在检测数据传输的误差上发挥着重要的作用[1]。CRC校验被用在PCI-Express总线、以太网(IEEE 802.3)以及WiFi(IEEE 802.11)等通信标准中[2]。通常使用的CRC校验生成算法有串行的线性反馈移位运算LFSR[3-4],但随着数据传输速率的提高,使用串行运算不能满足系统的要求[5],有必要实现并行CRC计算模块。

对于数据字节流{Cn(x),…,C1(x),C0(x)},Ck(x)都是关于x的7次多项式,表征一个字节的数据;生成多项式记作G(x),为关于x的N次多项式。CRC校验结果为:

考虑到有限域GF(2)上的加法等效于XOR异或运算,而乘法等效于AND与运算,在FPGA上可以实现一种基于矩阵式数据选通的并行CRC运算模块。其结构框图如图2所示。该并行CRC运算模块包含有逻辑运算阵列和输出寄存器两个部分。其中逻辑运算阵列由组合逻辑构成,其功能包括:将收到的数据DataIn左移(N-8)位,得到N位数据 利用

利用 与上次CRC运算结果Rk(x)进行XOR运算,得

与上次CRC运算结果Rk(x)进行XOR运算,得 运算结果进入数据选通运算阵列,阵列由(N×N)个1-bit选择器和N个N-bit XOR运算单元构成,选通使能信号是通过计算Φ=(A+KB)8结果得到的;阵列出来的运算结果进入输出寄存器,由时序逻辑构成,在模块接收到ENA使能信号时,寄存逻辑运算阵列的结果输出到Q;当输出寄存器接收到RST复位信号时,CRC模块的输出Q相当于CRC校验初始值R-1(x)。

运算结果进入数据选通运算阵列,阵列由(N×N)个1-bit选择器和N个N-bit XOR运算单元构成,选通使能信号是通过计算Φ=(A+KB)8结果得到的;阵列出来的运算结果进入输出寄存器,由时序逻辑构成,在模块接收到ENA使能信号时,寄存逻辑运算阵列的结果输出到Q;当输出寄存器接收到RST复位信号时,CRC模块的输出Q相当于CRC校验初始值R-1(x)。

在本虚拟软盘设计中,取N=16,即进行CRC-16校验,生成多项式为G(x)=x16+x12+x5+1,根据定义得到K=[0 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1]T,计算状态转移矩阵Φ,得到选通使能阵列如表1所示。其中横向表示输入位,用十六进制表示相应的位下标;纵向的表示输出位对应的下标;表中阴影部分对应的输入位被选通,空白部分对应的输入位不被选通。

1.3 MFM编解码

1.3.1 MFM编码原理与实现

在软盘应用中,读写的数据都是以串行方式传输的。通常在各个数据位之间插入时钟位,保证数据能被正确传输和识别[6]。在软盘的数据传输中,采用MFM编码。其表达式如下:(x,y,z)→(x,x NOR y,y,y NOR z,z),其中NOR为非或运算,即p NOR q=p∨q。在RData和WData信号线上,一个电平翻转表示在MFM编码码流的时钟位或者数据位中出现了“1”;而没有翻转,则表示在码流的时钟位或数据位中出现了“0”。采用500 kb/s的传输速率,一个数据位的传输需要消耗2 μs时间。图3为4-bit数据流“1010”MFM编码示意。

MFM编码没有起始标志,所以在每个扇区地址段和数据段之前都有AM域,其中的数据字节“0xA1”的编码采用了MMFM编码,用于标记码流起始:在数据位中,若出现连续的0-0,则时钟位变1;若出现0-0-0,则时钟位是1-0;若出现0-0-0-0,则时钟位是1-0-1;以此类推。

图4是MFM编码模块的结构框图。整个MFM编码过程由移位寄存模块、核心编码模块、计数模块和并行转串行模块组成。其中,移位寄存模块保留上一字节数据的最低位和当前字节数据,生成数据mfmData用来传递给核心编码模块进行MFM编码。核心编码模块根据MFM编码规则,对mfmData进行编码运算,并通过Violate信号判断当前是否处于AM域,若是,则要使用MMFM编码规则。计数器模块用来生成BitCnt计数信号,传递给并转串模块,生成最后的数据比特流mfmBit信号。

1.3.2 MFM解码原理与实现

数据在编码和传输过程中,经常出现相位超前、延迟的情况。在MFM解码之前,需要先同步WData码流和MFM解码时钟。此外,软盘数据在AM域的0xA1标志遵循MMFM编码,用于定位MFM码流的起始位置。图5是MFM解码模块的模块结构框图。采用32 MHz的采样时钟捕捉WData信号。因为一个数据位周期为2 μs,采样过程中计数器由0计到63,即T=0,1,2,…,62,63。据此设定数据比特的采样时间在T=10和T=42时刻采样结果保存在移位寄存器SHIFTER中,并分离数据位和时钟位。MFM码流中的下降沿出现通常在T=0或者T=31时刻。AM域的数据字节0xA1经 MMFM编码后CLOCK_BITS是0x0A,而MFM编码后CLOCK_BITS为0x0E。据此,仲裁单元的相位调整规则如下:

(1)检测到WData下降沿时:若16≤T≤47,选通T=31;若T≤15或者T≥48,选通T=0;

(2)若DATA_BITS==0xA1且CLOCK_BITS ==0x0A,即检测到0xA1编码违例,则选通T=44;

(3)否则选通T=T+1。

最后,数据比特计数模块用来判断是否接收到8 bit数据,若是,则输出数据有效脉冲信号MFM_DATA_EN。

2 虚拟软盘系统的设计与实现

2.1 虚拟软盘系统框架结构

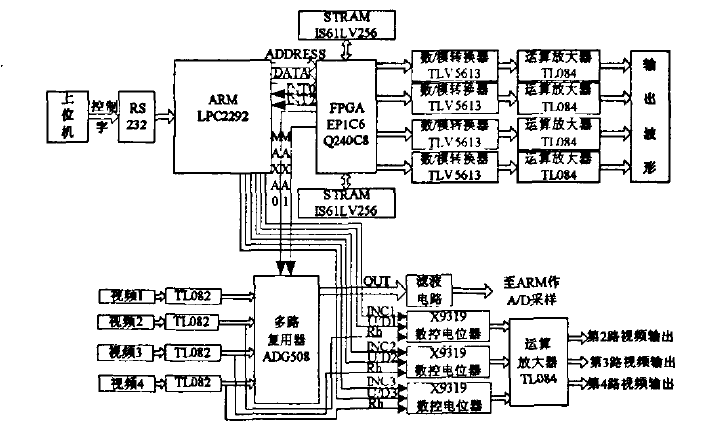

虚拟软盘系统如图6所示。其中,控制电脑与虚拟软盘系统处于同一个局域网下,通过socket通信实现与虚拟软盘系统的交互,包括软盘状态获取、软盘状态修改、发送软盘镜像和选择软盘镜像等命令;虚拟软盘系统包括ARM、FPGA和SRAM存储器3个部分,其中ARM和FPGA的交互通过SPI接口实现;ARM负责网络交互,从网络获取软盘数据、状态的读写命令,同时开启SSH服务,方便远程登录,开启FTP服务用于控制中心发送、选择虚拟软盘系统中的软盘镜像;FPGA负责将2 MB容量的SRAM虚拟成1.44 MB软盘,并通过软驱线和外部的台式机/织布机进行交互。

2.2 FPGA部分的结构

FPGA部分的结构框图如图7所示。该系统主要包括虚拟软盘控制模块、SPI收发模块、SRAM控制模块。

控制模块实现软盘磁针的位置控制和数据编解码:步进模块通过检测iStep下降沿和iDir电平确定当前软盘磁针所处的磁道号rCylNo;通过iHdSel电平确定磁针所处柱面号rHeadNo;旋转模块确定当前扇区号rSectNo以及在扇区内偏移地址rAddrL。MFM解码模块根据WData得到回写数据wData和磁道wCylNo、柱面wHeadNo、扇区号wSectNo及扇区内偏移地址wAddrL等信息。

通过SPI收发模块,FPGA可获取到ARM给出的读写命令,数据交换模块会根据命令判断执行以下某个行动:读取软盘的扇区数据、修改软盘的扇区数据、获取软盘状态(写保护,软盘就绪,写入使能,磁道、磁面和扇区等)、修改软盘状态(写保护和软盘就绪等)。

地址、数据等信息通过地址转移模块,映射成对SRAM的读地址rAddr和写地址wAddr。通过SRAM读写控制模块,可以对虚拟成软盘的SRAM进行数据访问。CRC编码模块用于计算地址段和数据段的校验和,可以用来检测数据传输上可能出现的错误。软盘数据或者校验和经过MFM编码模块生成MFM码流传送给台式机。

2.3 ARM程序结构

ARM部分的程序设计框图如图8所示。其中,主线程负责socket和SPI接口的初始化,并创建线程1和线程2;线程1负责通过网络获取控制中心的命令(包括软盘状态读取命令即#R,软盘状态修改命令即#W、WP、READY、FLAG,以及镜像文件读取/写入命令即&R/W、xxx.ima),对互斥量filelock进行上锁后,修改data_sent为1,再把filelock解锁;线程2负责判断data_sent是否为1,即网络命令是否有效。若是,则对filelock进行上锁后,根据网络命令执行相应的操作,并返回相应数据给控制中心,再将data_sent清零后,把filelock解锁;若data_sent为0,即没有收到网络命令,那么读取当前软盘状态,空闲1 s后,重新进行循环。

此外,ARM端还负责作为FTP服务器,用于接收控制中心发送的各个ima软盘镜像文件。

3 虚拟软盘运行测试情况

针对提出的虚拟软盘设计方案进行测试与验证。在Altera的DE2-115开发板上烧写FPGA工程文件,并在树莓派上运行ARM部分的程序。对虚拟软盘的测试包括虚拟软盘格式化、文件读写、镜像制作、启动盘测试等。首先对虚拟软盘彻底格式化,将虚拟软盘所有扇区数据清零;然后进行多文件随机写入,并读取虚拟软盘文件,进行文件比较,比对结果说明虚拟软盘读写正常;最后,制作启动盘并利用UltraISO制作软盘镜像,通过启动测试程序加载镜像,能顺利进入系统,说明启动盘制作和读取正常。

4 结论

本文提出并实现了一种基于FPGA和ARM的虚拟软盘方案,并成功将2 MB的SRAM虚拟成1.44 MB软盘,可通过网络对虚拟软盘的状态和数据进行远程访问,也可通过台式机对虚拟软盘进行读写操作。利用实际开发板进行实验,验证了本设计方案的可行性。

-

FPGA

+关注

关注

1663文章

22493浏览量

638951 -

ARM

+关注

关注

135文章

9583浏览量

393490 -

编码

+关注

关注

6文章

1040浏览量

57118

发布评论请先 登录

关于quartus虚拟按键的问题

VxWorks 系统启动

FPGA板卡能实现虚拟化图形界面吗

怎么实现基于FPGA的低成本虚拟测试系统的设计?

ARM的虚拟化技术是什么?如何去实现呢

一种基于FPGA技术的虚拟逻辑分析仪的研究与实现

基于FPGA的虚拟测试系统实现

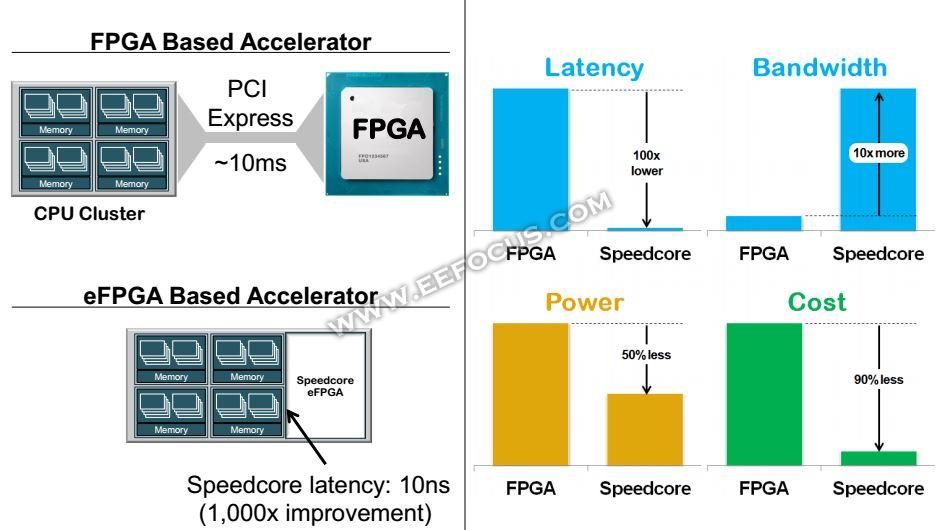

关于MPU, FPGA SoC以及eFPGA

基于FPGA的ARM并行总线和端口设计

如何使用FPGA和ARM设计和实现多路视频采集系统

关于基于FPGA和ARM的虚拟软盘实现

关于基于FPGA和ARM的虚拟软盘实现

评论