JESD204B是什么

JESD204B是一种新型的基于高速SERDES的ADC/DAC数据传输接口。随着ADC/DAC采样速率的不断提高,数据的吞吐量也越来越大,对于500MSPS以上的ADC/DAC,动辄就是几十个G的数据吞吐率,而采用传统的CMOS和LVDS已经很难满足设计要求,这个时候,JESD204B应运而生。现在各大厂商的高速ADC/DAC上基本都采用了这种接口。

使用JESD204B接口的原因

◾ 不用再使用数据接口,时序控制简单

◾ 不用担心信道偏移

◾ 不用再使用大量IO口,布线方便

◾ 多片IC同步方便

◾减少了PCB布板空间

◾减小了器件的引脚和封装大小

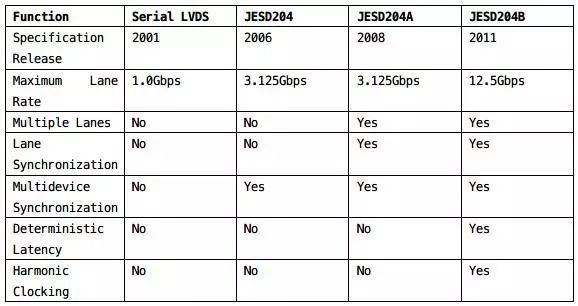

JESD204B与其他接口的对比表

JESD204B种类

JESD204B包括3个子类,分别是子类0,子类1,子类2。三个子类主要是根据同步方式的不同划分的。子类0兼容JESD204A,子类1使用SYSREF同步,子类2使用SYNC进行同步。只有子类1和子类2支持确定性延迟——发送端到接收端之间的链路延迟固定。

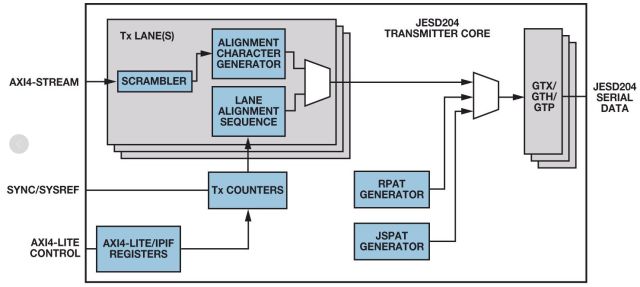

分层规范

大部分的ADC和DAC都支持子类1,JESD204B标准协议中子类1包括:传输层,链路层,物理层。在少部分资料中也会介绍含有应用层,应用层是对JESD204B进行配置的接口,在标准协议中不含此层,只是为了便于理解而添加的一个层。传输层负责将采样数据映射为数据帧。链路层负责链路的建立,数据传输。物理层负责数据的发送和接收。

01

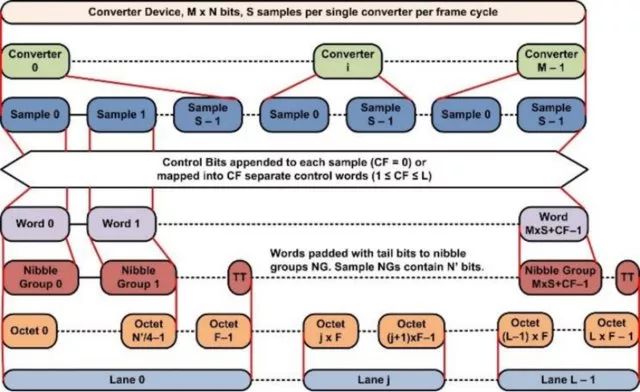

传输层

数据传输层的主要功能将AD转换器采样的数据映射成8bit位宽的字节数据。先将所有的采样数据线性的排开,然后添加控制字和控制位得到words,也可以选择不加控制字和控制位,则words和之前排列的采样数据相同,添加控制字和控制位有两种方法,第一种在每一个采样点的末尾添加控制位;第二种不在采样点末尾添加控制位,在所有采样点的末尾添加一个控制字,控制字里面的控制位对应前面的采样点。通过添加tail将words进行扩展,使每一个word的位数为N位,这个值是4的倍数,控制字不需要扩展。最后将数据划分得到L*F个字节,对应L个通道。

02

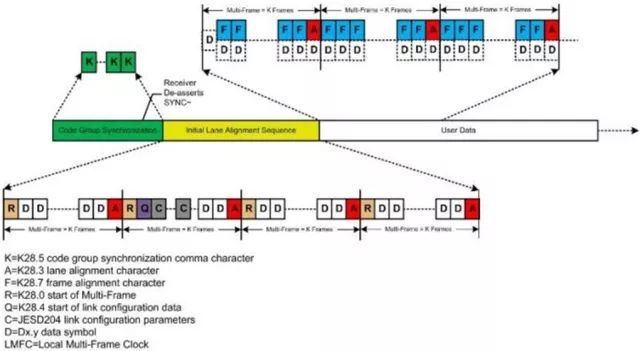

链路层

链路层主要包括扰码器加扰,链路建立,8b/10b编码三部分。链路建立主要包括代码组同步(CGS),初始通道对齐序列(ILAS),用户数据。

03

物理层

在物理层中,数据进行串行化,8B/10B编码数据以线路速率发送和接收。物理层包括串行/解串器(SERDES)模块、驱动器、接收器和CDR。由于数据传输速率非常高,这些模块常常采用定制单元设计。JESD204和JESD204A均支持最高3.125 Gbps的速度。JESD204B规范支持三种可能的速度等级。速度等级1支持最高3.125 Gbps的速度,基于OIF-SxI5-0.10规范。速度等级2支持最高6.375 Gbps的速度,基于CEI-6G-SR规范。速度等级3支持最高12.5 Gbps的速度,基于CEI-11G-SR规范。

JESD204B缺点

JESD204B也有其不足之处,首先是增加了接口的传输延时,其次是其需要特殊的时钟电路导致更复杂的电路设计。

关于JESD204B串行接口时钟需求及其实现方法敬请关注下期文章。

-

adc

+关注

关注

98文章

6489浏览量

544418 -

物理层

+关注

关注

1文章

148浏览量

34350 -

JESD204B

+关注

关注

5文章

76浏览量

19124

原文标题:五分钟让你认识JESD204B

文章出处:【微信号:gh_873435264fd4,微信公众号:FPGA技术联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

JESD204B的系统级优势

JESD204B串行接口时钟的优势

如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?

如何采用系统参考模式设计JESD204B时钟

JESD204B协议介绍

JESD204B的优势

JESD204B SystemC module 设计简介(一)

JESD204B标准及演进历程

JESD204B使用说明

JESD204B是什么?JESD204B种类

JESD204B是什么?JESD204B种类

评论