声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS1220

+关注

关注

24文章

488浏览量

125196

发布评论请先 登录

相关推荐

ADS8472采样率可调吗?

问题如下:

1、ADS8472手册中第一页的features里写到“0 to 1-MHz Sample Rate”,是不是指这款adc采样率可调?我没有在手册里看到可调的方法。

2,、待采信号叫S

发表于 12-25 08:29

采用STM32读ADS1198数据,采样率不受控制是怎么回事?

采用STM32读ADS1198数据,读取的数据很正常,配置寄存器,配置采样率为500SPS,采500个点时间理论为1S,我却花了4S;配置成1K采样率,采500个点时间比之前稍微少了点,但也是4S

发表于 12-13 08:38

ADS1292R采样率与预期不符,为什么?

高电平, 250, 500采样率下也是每10秒比预期少3-4次DRDY。中断和循环读取的方式都试过。ADS1292R是数据连续读取模式.

请帮忙分析一下,非常感谢!

发表于 11-20 06:15

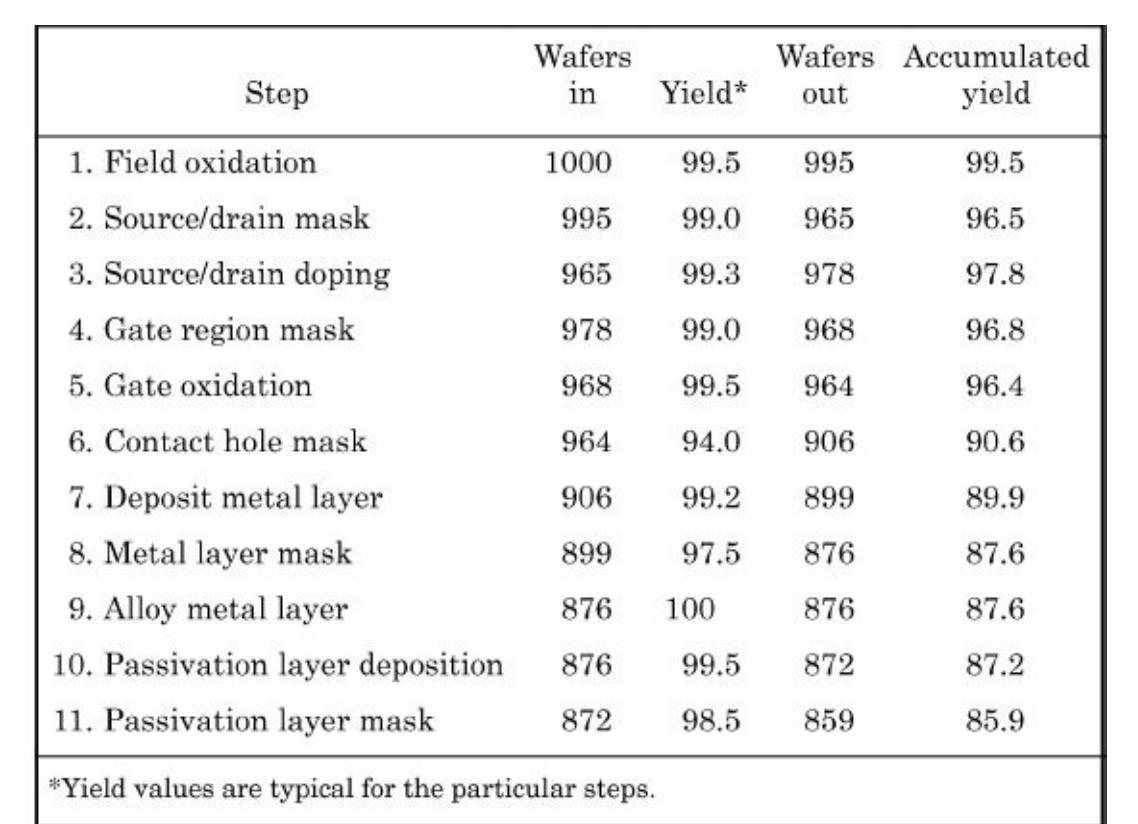

浅谈影响晶圆分选良率的因素(2)

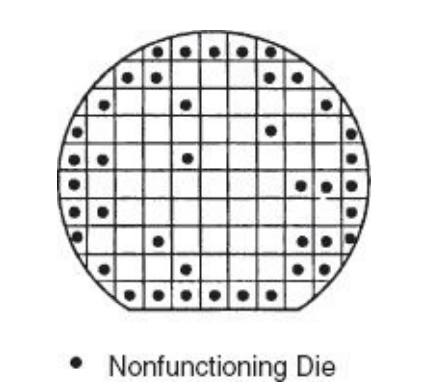

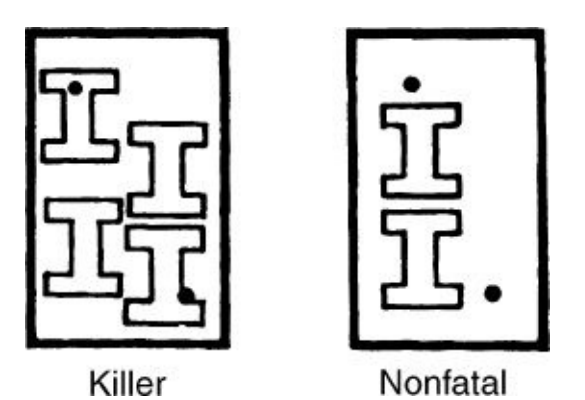

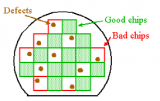

在晶圆制造良率部分讨论的工艺变化会影响晶圆分选良率。在制造区域,通过抽样检查和测量技术检测工艺变化。检查抽样的本质是并非所有变化和缺陷都被检测到,因此晶圆在一些问题上被传递。这些问题在晶圆分选中显现为失败的设备。

晶圆制造良率限制因素简述(2)

硅晶圆相对容易处理,并且良好的实践和自动设备已将晶圆断裂降至低水平。然而,砷化镓晶圆并不是那么坚韧,断裂是主要的晶圆良率限制因素。在砷化镓制造线上,电路的售价很高,通常会处理部分晶圆。

广立微INF-AI助力格科微产品良率提升

AI技术在半导体设计、制造和优化等方面的应用日益深入。在设计阶段,AI可以通过机器学习算法,提高芯片性能和能效。在制造过程中,AI用于预测和检测缺陷,优化生产流程,快速提升良率。同时AI模型可以分析

半导体工艺之生产力和工艺良率

晶圆实际被加工的时间可以以天为单位来衡量。但由于在工艺站点的排队以及由于工艺问题导致的临时减速,晶圆通常在制造区域停留数周。晶圆等待的时间越长,增加了污染的机会,这会降低晶圆分选良率。向准时制制造的转变(见后面章节)是提高良

传三星电子12nm级DRAM内存良率不足五成

近日,据韩国媒体报道,三星在其1b nm(即12nm级)DRAM内存生产过程中遇到了良率不足的挑战。目前,该制程的良率仍低于业界一般目标的80%~90%,仅达到五成左右。为了应对这一局

广立微和坤锐电子在良率数据管理分析业务领域达成合作

近日,半导体数据分析领域的佼佼者广立微(Semitronix)与RFID硬件解决方案的领先企业上海坤锐电子(Quanray)达成战略合作。此次合作旨在良率数据管理分析领域,共同推动半导

三星3纳米良率不足60%

三星近年来在半导体制造领域持续投入,并力争在先进制程技术上取得突破。然而,据韩媒报道,三星在3纳米制程上的良率问题似乎仍未得到有效解决,这对其在市场上的竞争力构成了一定的挑战。 据百能云芯电子.元器

Mini LED良率超99.9999%+ 大为技术材料厂商打响良率“攻坚战”

在Mini/Micro LED火热度狂飙的今天,Mini/Micro LED应用存在产品良率低、成本高等现象。

ADS中文基础教程(良率分析)

ADS中文基础教程(良率分析)

评论