昨天在调试Lattice EVDK开发板上的DDR3 Demo时,遇到一个莫名其妙的问题,今天来总结一下,并与大家分享。

一、问题描述

在Demo的顶层文件ddr3_test_top.v中有如下几句话:

inputtest1; outputout_test1; assignout_test1=test1;

且test1和out_test1与Design中的其他逻辑没有任何的关系,然而,当我把它删除的时候,却发现原本运行正常的Demo却出错了!!!

于是乎,先去检查这两个引脚是否和硬件相关,在LPF文件中找到其相关约束:

LOCATECOMP"test1"SITE"F5"; IOBUFPORT"test1"IO_TYPE=SSTL15_I; LOCATECOMP"out_test1"SITE"B1"; IOBUFPORT"out_test1"IO_TYPE=SSTL15_I;

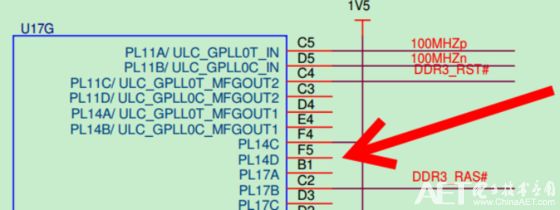

然后查看EVDK开发板的原理图:

握草,这是什么鬼?

于是乎,进一步做测试,把test1和out_test1替换为其他的引脚试试看呢。结果发现:当test1在Bank7上时,Demo功能正常,当test1不在Bank7上时,功能则不正常!

想了好久,奈何我这种小菜鸟却怎么也想不明白,于是请教了大牛!

二、问题分析

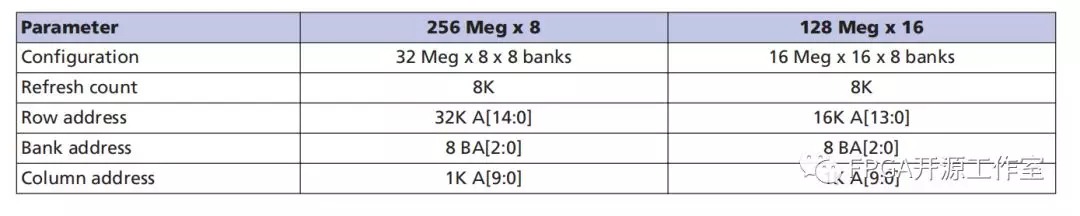

首先,还是检查原理图和LPF文件,由于EVDK板子上有两个Mircon的DDR3的内存颗粒,且均为x16的Configuration。也就是DQ的宽度为16bit,两个颗粒合并为32bit的DQ。其中颗粒一对应DQ0~DQ15,颗粒二对应DQ16~DQ31。DQ0~DQ15连接到了Bank6上面,而DQ16~DQ31连接到了Bank7上面。但是需要注意的是,一些控制信号(如RST、CS、WE、DM等)则分布在Bank6和Bank7上,换句话说,即使Design中只需要使用一个DDR3颗粒,也需要同时使用Bank6和Bank7。

因为DDR3采用的是SSLT15 I电平标准,所以需要设置Bank6和Bank7的VREF。在LPF文件中,我们可以找到:

LOCATEVREF"BANK_6_VREF"SITE"V4"; LOCATEVREF"BANK_7_VREF"SITE"J7";

检查原理图,发现V4和J7引脚也正确地连接到了参考电压上。

此时,我们再次将上文提到的ddr3_test_top.v中的test1和out_test1相关的几条语句删除,并删除LPF文件中的相关语句。

然后从新综合、MAP,并PAR,此时在PAR的报告中可以发现如下的警告:

WARNING - par: LOCATE VREF "BANK_7_VREF" preference has been ignored, because no PIO in bank "7" uses this VREF.

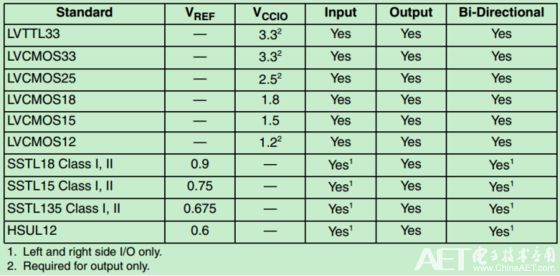

也就是说Diamond认为,我们的Design中并没有使用Bank7中的PIO,所以不需要VREF,并忽略了LPF文件中给出的约束。所以Bank7的VREF引脚并未被设置为VREF模式,而是作为普通IO的(默认模式)。但是DDR3使用的是SSLT15 I电平标准,需要VERF引脚为其提供0.75V的参考电压(一般使用1.5V的VCCIO分压即可),如下图所示:

检查ECP5数据手册,发现如下一句话:

The VREF voltage is used to set the threshold for the referencedinputbuffers, such as SSTL.

注意是input!这就解释了为什么当test1引脚分配在Bank7上可以,分配在其他引脚上就不行的原因了。因为如果Bank7上没有input的话,Diamond就会认为此时为Bank7设置VREF是没有必要的,所以也就忽略了LPF中的约束。

难道是ECP5的数据手册写错了?难道是DDR的output也需要VREF?

其实不然,再次检查EVDK板的原理图,发现Bank6和Bank7的VREF实际上连接的是同一个电压(换句话说,这两个VREF是直接连在一起的)。但是合理的硬件设计方式是,不同Bank的VREF独立(即不要连接在一起)。也正是这种不合理的设计方式,导致了本文所讨论的问题。

在我们的设计中实际上只需要给Bank6设置VREF即可,Bank7实际上是不需要的,但是为什么不给Bank7 VREF的话,DDR却不能正常工作呢?原因在于,如果Bank7的J7引脚(VREF1_7)没有被配置为VREF输入模式的话,其默认为上拉的。而J7引脚(VREF1_7)的上拉会影响到VREF的电压,进而影响到Bank6上的V4引脚(VREF1_6)的VREF输入,最终导致Bank6没有稳定有效的VREF,因此DDR不能正常工作。

为了让J7引脚(VREF1_7)不影响VREF的电压,显然最好是将其也设置成VREF输入模式,为了防止我们的设置被Diamond优化掉,才出现了本文前面所讨论的这一问题。

三、关于SSTL电平(更新内容)

这里来分析一下为什么DDR3的相关IO的输入需要参考电压,而输出却不需要。DDRx SDRAM普通IO采用的是SSTL电平标准(clk和dqs等采用的是SSTL的差分版本SSTLD),而SSTL实际上是一种伪差分电平。

所谓伪差分电平,就是信号的接收端是一个差分的接收器,但是其中一端固定接参考电压VREF,而另一端接单端信号线。输入信号电压与参考电压之间进行比较,作为判决输入信号高低的标准。而伪差分标准的输出驱动器则是单端信号标准中常见的推挽式的结构(Push-Pull),显然是不需要参考电压VREF的。

由于伪差分电平的信号输出的摆幅较小,瞬态的电流较小,保持信号完整性要相对容易些。因此,这种电平主要应用在高速的存储器接口中,如DDRx SDRAM、QDR SRAM和RLDRAM等中。

这种结构的好处是,其输入信号只需要在VREF上下小幅度摆动即可被输入驱动器正确地接收。这样信号的噪声余量就很大,信号能否被正确接收下来,VREF将起到关键作用,因此设计时需要保证VREF较高的精度。

-

电平

+关注

关注

5文章

360浏览量

39883 -

开发板

+关注

关注

25文章

5032浏览量

97375

原文标题:【博文连载】EVDK DDR3 Demo调试笔记(关于VREF的问题)

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

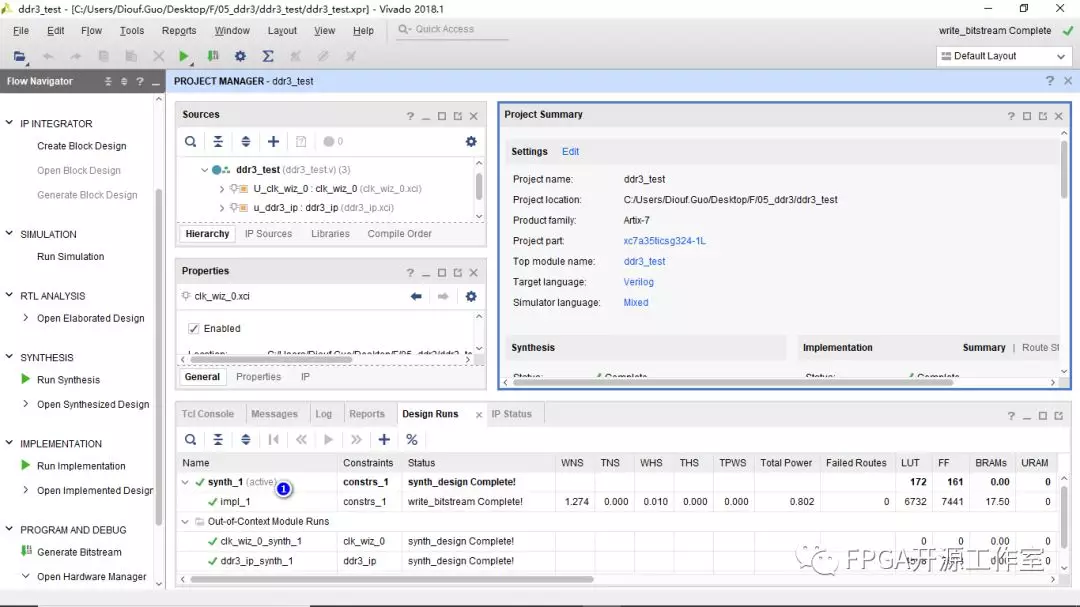

基于Digilent的Arty Artix-35T FPGA开发板的DDR3读写控制

基于Arty Artix-35T FPGA开发板的DDR3和mig介绍

如何提高DDR3的效率

【创龙TMS320C665x DSP开发板】DDR3加载程序的问题与解决方法

6678开发板DDR3布线约束的问题

6657的DDR3初始化不成功

【Combat FPGA开发板】配套视频教程——DDR3的读写控制

紫光同创FPGA入门指导:DDR3 读写——紫光盘古系列50K开发板实验教程

基于FPGA的DDR3 SDRAM控制器用户接口设计

安捷伦科技推DDR3协议调试和测试套件,具备最齐全的行业功能

lattice DDR3 IP核的生成及调用过程

调试Lattice EVDK开发板上的DDR3 Demo时的问题

调试Lattice EVDK开发板上的DDR3 Demo时的问题

评论