在运放的使用中,最初级的硬件设计者的想法就是只有增益倍数这一个参数。当然这是运放的基本能力,但是显然只知道放大倍数是不能说其会使用运放的。或许你知道运放,知道差分放大是放大差分信号的,甚至还知道共模抑制比。

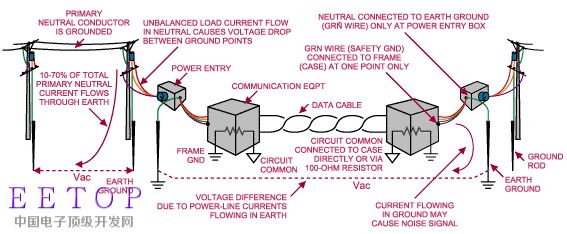

这是一个典型的信号传输系统:

我们可以看出这个系统里重要的一点是子系统的参考电位,运放的共模电平也是参考电压的问题。运放的共模电压定义为:

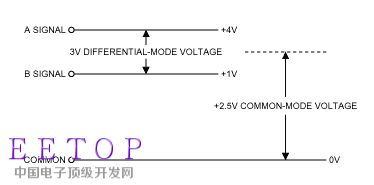

计算公式Vcm=(Va+Vb)/2,可以理解为差分运放的差分两端信号的中间电位点。

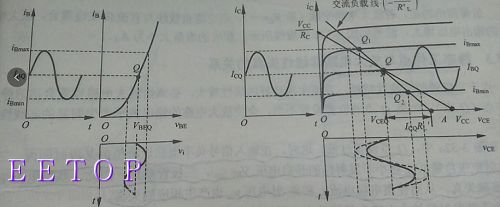

那么运放的共模电平意义在哪里?这个可以回溯到三极管的放大电路中:

晶体管的放大需要配置静态工作点,也就是需要设置偏置电压让放大器处于放大状态而不是饱和或者截止状态。因此我们对于交流信号放大需要提供偏置电压,而对于双电源运放来说,共模电压0V也是其共模电压。因此,我们可以看出,我们是不需要对共模电压放大处理的,共模电平的作用就是提供一个“平台”。

共模电压与噪声:

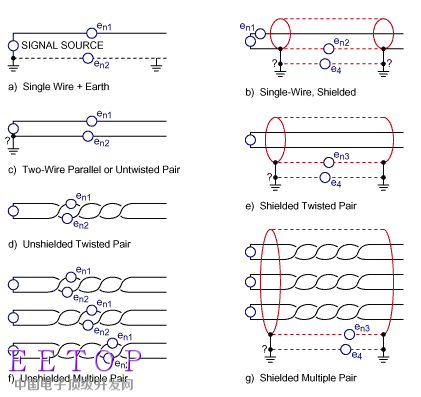

其实第一张图就体现了共模电压的干扰问题,参考电位的差异会导致共模电平差异,对于信号检测系统而言,干扰来源有来自附近电场的容性耦合,来自附近磁场的感性耦合,以及空间辐射信号的电磁耦合。下图是信号线缆的几种干扰特点,我们可以采用双绞线和屏蔽的方式处理一些干扰。

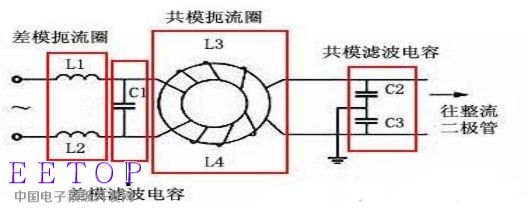

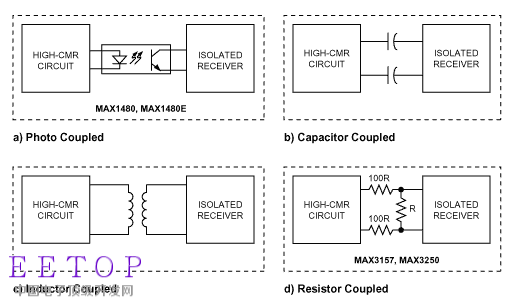

下面是针对传输线的共模干扰的抑制方式:利用抑制器件以及隔离。

例如我们在处理交流信号放大时,经常通过电容隔离直流电平,避免影响后级的共模输入。

对于参考电位带来的共模干扰也可以通过电源隔离的方式,形成两个相对独立的电源系统。

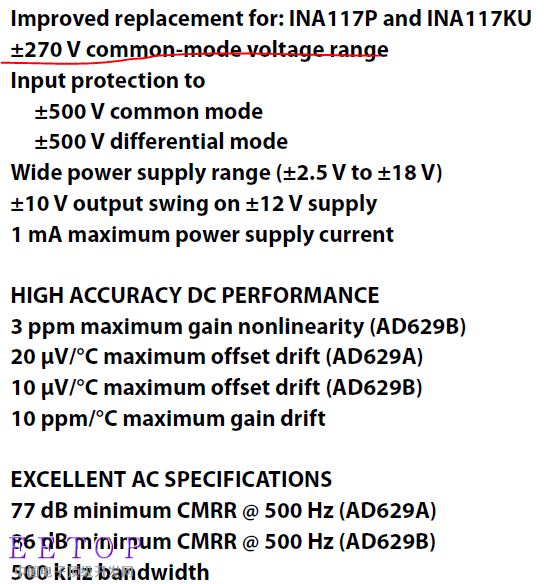

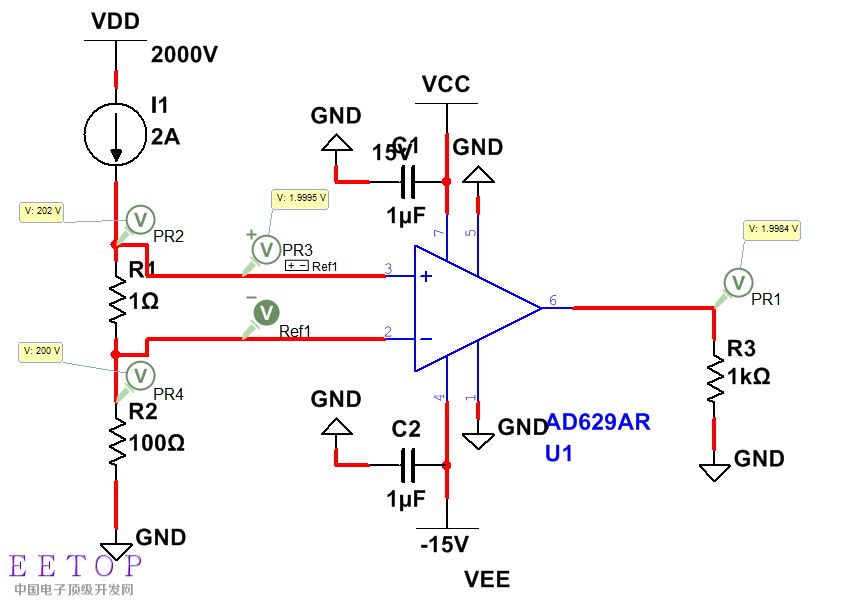

最后介绍一下高共模电压的检测系统,这一点在BMS中应用较多,我们需要对串并联的电池组进行电压监测,就会有高共模电压达到数百V出现。而一般运放的共模电压输入也就比电源小。

这里介绍一种专用的差分检测运放,以AD629为例:

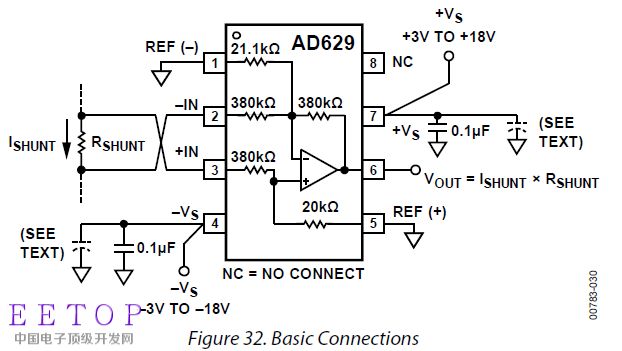

运放的内部结构比较简单:

看起来我们其实可以直接用普通运放来做,但是事实上我们可以看到对于上百V的共模信号进行差分检测,如果反馈电阻不匹配,就会导致共模转差模输出,极大影响输出电压,其实就是共模抑制的问题。尤其是检测电流很小的情况下输出电压在mv,而集成芯片内部的电阻因为半导体的制造工艺可以保持很好的匹配度。

下图是共模抑制性能:

小结:说来也简单,运放的共模电压就是运放输入的一种形式而已,重要的是我们需要明白它的影响和作用。

-

运放

+关注

关注

47文章

1160浏览量

53057 -

共模电压

+关注

关注

2文章

101浏览量

12641

原文标题:硬件开发者之路之运放共模电压的解释

文章出处:【微信号:eetop-1,微信公众号:EETOP】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

共模电平对于运放以及信号系统的意义

共模电平对于运放以及信号系统的意义

评论