Wishbone名字的由来

根据美国韦伯斯特(Webster,1758—1843,美国词典编辑家)词典,WISHBONE是指大多数鸟类胸骨前的一块叉状型的锁骨。在名字定义初期,Silicore公司设想找一个能够反映双向总线这一特点的名字。这些总线是由多路选择器和三态门实现的,它们的形状类似Y,和锁骨(WISHBONE)相似,所以后来被称为WISHBONE总线。这个名字是由Wade Peterson,一名Silicore公司的工程师,在当年美国感恩节上提出的。

一般总线规范的共同特点

同时适用于于软核、固核和硬核设计;对开发工具和目标硬件没有特殊要求,并且几乎兼容已有的所有综合工具;可以用多种硬件描述语言来实现;支持结构化设计方法学,以提高大团队的设计效率;灵活的数据和地址总线宽度,支持大端和小端操作;支持主从设备接口,支持多主设备,这是片上共享总线通信所必须的,多个主设备同时需要进行总线操作时,由仲裁器决定当前哪个主设备可以使用总线,仲裁逻辑用户可以自行定义。

Wishbone总线的特点

·简单、紧凑,只需要很少的逻辑门就可以实现Wishbone的IP核的设计;

说明:熟悉AMBA总线的读者在读完本章后就能够理Wishbone比AMBA总线简单的多,但是两者各有个的优势。AMBA将所有的外设分为高速设备和低速设备,高速设备连接到系统总线,通常通信的数据量也较大,如SDRAM控制器、NAND Flash控制器、LCD控制器,低速设备连接外设总线,通常通信数据量小,如通用串口、计时器等。外设总线与系统总线通过总线桥接器相连。在实际系统中,处理器、系统总线、外设总线间的时钟频率的典型比值之一是4:2:1,因此整个系统的功耗被有效降低。另外一个好处是通过在总线桥接器中添加DMA引擎,系统总线和外设总线可以实现速率解耦。而依照Wishbone规范,Wishbone总线上所有设备都要连接到同一总线,无论是高速设备还是低速设备。与Wishbone总线相比,AMBA的缺点是设计较为复杂。但是实际上,Wishbone总线也设计为类似AMBA总线的架构,但此时系统为双Wishbone总线架构。

·支持大型项目所需要的结构化设计;

·数据传输模式包括:单次读写模式、块读写模式、RMW模式;

·可调整的数据总线宽度,最高可达64位;

·支持大小端模式;

·支持点对点模式、共享总线模式、switched fabric模式等连接方式;

·握手协议允许每个IP核调整数据传输速度;

·支持单时钟数据传输;

·支持正常周期结束、重试、以及周期错误。成功是操作的正常结束方式,错误表示操作失败,造成失败的原因可能是地址或者数据校验错误,写操作或者读操作不支持等。重试表示从设备当前忙,不能及时处理该操作,该操作可以稍后重新发起。接收到操作失败或者重试后,主设备如何响应取决于主设备的设计者;

·可调整的地址宽度;

·从机(SLAVEs)允许从设备进行部分地址解码,有利于减少了冗余地址译码逻辑,提高地址译码速度;

·支持用户定义的标签。这些标签可以用于为地址、数据总线提供额外的信息如奇偶校验,为总线周期提供额外的信息如中断向量、缓存控制操作的类型等。Wishbone规范只定义标签的时序,而标签的具体含义用户可自行定义。支持用户定义的标签是Wishbone规范区别与其他片上总线规范的重要特征之一;

·支持点对点、共享总线、Crossbar switch、数据流连接、片外连接等IP连接方式;

·同步化设计,包括复位方式;

·不依赖任何硬件设计技术(FPGA、ASIC等)、IP类型(软核、固核和硬核)、综合工具、布局布线工具和硬件测试技术等。

总结以上内容,Wishbone总线规范区别于其他总线规范的两个核心特点是:

·是轻量级规范,因此接口更加简单紧凑;

·支持支持用户定义的标签。

-

总线

+关注

关注

10文章

2877浏览量

88043 -

Wishbone

+关注

关注

0文章

16浏览量

10423

原文标题:【博文连载】Wishbone总线标准介绍

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

i2c总线规范

电源管理总线规范

电源管理总线规范

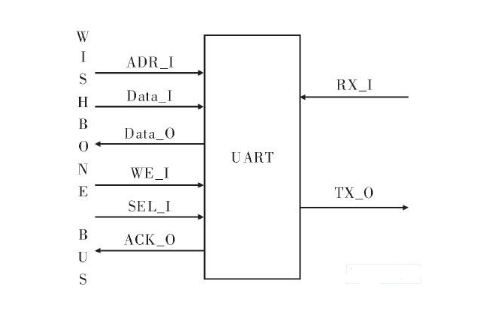

基于Wishbone片上总线的IP核的互联

基于WISHBONE总线的FLASH闪存接口设计

Wishbone一般总线规范的共同特点

Wishbone一般总线规范的共同特点

评论