在先进工艺节点半导体制造中,工艺和器件的变异性越来越不可忽视。在半导体制造的工艺站点,先进工艺控制(APC)已经广泛应用于减小和优化工艺和器件变异性(批次间,晶圆间,芯片内),增加制造稳定性,减少制造成本。这些制造性变异同时也会影响晶圆良率和产品特性。晶圆级针测(Chip Probing)位于半导体制造工艺完成之后,能否在晶圆针测阶段调整芯片电路特性,以便进一步抵御先进工艺中的制造性变异,成为芯片产品设计以及 DFY/DFT 良率提升设计的热点之一。针对晶圆级针测中,在电路参数调整测试中应用 APC 原理,提出先进测试控制(ATC)理念,通过 ATC 算法优化传统 CP 的参数调整测试,大大减少晶圆针测的时间和成本,保证了晶圆针测覆盖率和产品良率。

1 引言

随着工业及消费类电子对低功耗、高速度规格的需求提高,推动半导体工艺的摩尔定律持续演进(65 nm,40 nm,28 nm……)。器件尺寸持续微缩和性能的提升导致半导体制造工艺变异性(variation)管控和制造稳定性难度成倍增加,因此先进半导体产品的量产工艺窗口持续缩小正成为越来越大的挑战,如图 1 所示。

半导体制造中的工艺参数变异性是固有特性,光刻关键尺寸、薄膜厚度、器件掺杂浓度等工艺变异性大小,引起同一类器件参数分布变宽,如图 2 所示。65 nm 下的晶体管饱和电流比 130 nm 工艺的同一沟道宽度尺寸下的饱和电流离散度明显增加。这种工艺和器件的变异性会导致电路特性恶化甚至工作异常,对最终产品参数特性和良率产生直接影响[1]。

针对半导体制造工艺的固有变异性,半导体工业界在先进工艺节点普遍采用了 APC(Advanced Process Control)系统增加对工艺参数的控制。R2R 控制技术是半导体制造中广泛运用的一种过程控制方法[2,3], 减少重要工艺参数的制造变异性。

R2R(Run-to-Run)控制策略是针对间歇过程的基于模型的过程控制算法。在每个批次进行工艺过程前,根据历史工艺过程信息和当前晶圆信息,更能控制模型,动态调整晶圆加工的最佳配方,减少批次间的变异。半导体制造的 APC 控制系统一般以 R2R 策略为主,结合传统 SPC 管控和 FDC 技术,R2R 控制算法有指数加权平均移动方法(exponentially weighted moving average,EWMA)[4],模型预测控制( model predictive control,MPC)等,综合减少工艺制造变异性、降低成本、提升产品良率和生产效能。图 3 表示 R2R 控制结构图。

2 可编程 SoC 产品制造工艺和性能要求

高性能可编程 SoC 芯片(MCU、DSP、FPGA等)的应用场景越来越广泛,用于制造可编程 SoC 芯片的嵌入式闪存工艺也成为半导体制造的特色工艺之一[5]。嵌入式闪存的稳定操作需要一系列模拟电路模块来产生精确的模拟信号来保证闪存单元的正确操作和可靠性。 这些模拟信号包括:擦写高压、参考电压、参考电流等。工艺变异性会严重影响模拟电路的精度和重复性。随着闪存工艺的持续微缩,闪存单元的擦写窗口持续缩小,对于闪存操作的模拟电路精确性也提出了越来越高的要求。

对于嵌入式闪存 SoC 产品,除了半导体制造工艺中普遍采用 APC 系统减少工艺和器件变异性外,通常在闪存操作需要的模拟电路也会增加了良率提升设计(DFY/DFT),预留闪存操作辅助电路参数的调整区间,可以适度应对半导体制造变异带来的电路性能差异[6]。在晶圆级针测中通过自动测试机调整闪存工作的参数,以达到要求的闪存稳定操作条件。

以一个 55 nm 工艺上验证过的某嵌入式闪存产品为例,电路设计中可以预留出 32 个调整档位,按照每个档位 0.07 V 进行调整,这个 DFY 设计可以补偿目标范围内±1.1 V 的电路特性制造性变异。传统晶圆级测试中,都是针对每片晶圆、每个芯片单独进行电路参数调整,从档位边界开始全范围遍历,寻找符合目标的最佳档位,每个晶圆测试都是完全独立进行,无法利用晶圆历史基准数据,从而导致参数调整测试时间长,效率低下。

针对晶圆制造中存在批次间(lot to lot), 晶圆间(wafer to wafer)以及芯片内部(Die to die)的制造性变异,本文提出了晶圆针测的 ATC 理念和基本算法实现,基于已测试晶圆和芯片的历史产品特性数据进行分析,结合待测电路调整行为建模和预测,动态调整扫描边界和算法,减少了参数调整测试时间,提升了晶圆针测效率。

3 晶圆级参数调整 ATC 算法

晶圆级测试 ATC 流程图和组成元素可以简单表示为图 4 所示。

ATC 控制结构元素有下面几组。

(1)电路参数调整目标和行为模型。一般模拟电路参数如高压、参考电压和电流的 DFY/DFT 设计,这些电路参数 P 的变化是调整档位 x 的函数 f-(x)。 f-(x) 一般是单调的电路行为函数,此函数既可以呈线性或者非线性,通常在 DFY/DFT 设计阶段可以仿真和预估;参数调整目标设定为 tar,调整到 tar 时的 x 可以用 f-1(tar)表示:x = f--1(tar)。

(2)电路参数调整基准模型和控制算法。本例中暂时不考虑批次间变异,将晶圆间和芯片内变异分成两个反馈控制环,形成晶圆级针测的 ATC 参数调整自适应测试。电路参数调整模型和调整的档位可以用公式(1)和公式(2)表示。

X-i,j = f--1i,j (tar) (1)

S i,j = X-i,j - X-0 + 1 (2)

式中 i 为当前调整测试晶圆,j 为当前调整芯片,X-0 为扫描起点开始开始,tar 为调整目标,X-i,j 为目标调整档位,S i,j 为当前芯片的调整档位数。

传统参数调整的方法是全范围参数扫描,及每个芯片的 X-0 的有效范围都是 X-min ~ X-max。本文提出的电路参数调整算法中,X-0 不是一个固定值,而是一个动态更新的参考扫描起点 X-r。调整档位 S i,j 和当前参考扫描起点 X r (i,j) 可以表示为公式(3)和公式(4)。

S i,j = X-i,j- X r (i,j)(3)

(4)

jmax 为每片晶圆上芯片总数,当前待测芯片参数调整起点为 X r (i,j) 是上一片晶圆调整完成时的扫描起点 Xr(i-1,max) 和当前 i 晶圆已调整的芯片 j-1 实际调整档位 X i,j-1 等历史特性参数经过 ATC 反馈计算的动态值。公式(4)中 A 为工艺变异性对批到批与芯片到芯片电路参数的影响的权重。

(3)参数 ATC 扫描起点 X r 更新。初始化遍历参数和参数扫描边界;

(4)参数遍历算法控制器。基于参数调整的行为是否是线性、非线性,单调非单调,选择最优算法:一般针对单调的电路行为选择线性法遍历或者二分法查找,其算法复杂度为参数最大调整档位 X max 的函数 log2 (X max)。针对非单调电路行为,一般使用顺序查找调整空间是否存在目标匹配。

(5)在参数调整遍历过程中,通过自动测试机对电路参数档位 k 进行设定, 并且实时量测,参数调整空间遍历算法如图 5 所示。若遍历完成没有发现符合调整目标的档位, 则判断参数调整失败,分 Bin 并停止测试; 若发现符合目标的档位,调整成功。

(6)原位记录和反馈当前测试芯片的参数调整档位 X-i,j 以及参数测量值 M-(k),反馈供下一颗测试芯片进行参数调整约束条件更新。

(7)离线针对晶圆最优调整档位和参数值进行 SPC 管控和分析,定期校正 ATC 参数调整模型中的权重因子 A。这也可以作为半导体生产线基准线漂移的一个指标之一。

4 晶圆级参数 ATC 测试算法实现和效能分析

为了简单阐述 ATC 参数测试的理念,本文以一个即将进入量产的 55 nm 嵌入式闪存芯片的生产测试为例:此晶圆有 72 个验证芯片晶圆,需要在晶圆级测试中调节闪存擦写高压到 4.5 V,此电荷泵的输出高压调节函数 Vout = f(x)调节范围有 32 个档位,所以 x 有0,1,2, 3 … 31 个有效离散值。传统的参数扫描调整算法:每片晶圆总调整步数表示为 Stotal,扫描起点 x 从最小值固定值 Xmin 开始,每片晶圆总调整步数表示为公式(5)。

Stotal = ∑j Si,j = ∑jmaxj=1[ f i,j (tar) - Xmin +1 ] (5)

基于ATC 理念的参数调整算法总扫描步数可表示为公式(6)。

Stotal =∑j [X i,j - Xr(i,j)]

= ∑jmaxj=1[ f i,j (tar) - Xr (i,j) +1 ] (6)

根据图 4 和图 5 提出的晶圆级电性参数 ATC 反馈和调整算法,开发测试程式在某 55 nm 先进嵌入式闪存产品的擦写高压参数调整测试进行了试验。一片晶圆按照传统非 ATC 调整测试后的最终档位分布如图 6 以及图 7 所示。按照参数调整目标,最终此高压参数正确调整后档位集中在中位值 20,最大的档位为 25, 最小的档位为 18,如表 1 所示。

按照公式(5)和公式(6),在实验晶圆上传统参数调整方法和测试开销为 1 487 步, 而基于 ATC 算法调整的测试开销为 249 步,同比节省 1 238 步,节省比率达 83%,如表 2 所示。

在同等晶圆针测条件下,参数调整步数的减少可直接等效于单位测试时间的减少。 因此 ATC 理念的参数调整测试的效能较传统测试方法将显著提升。在大规模量产测试的情况下,产品模拟参数的调整测试有多个项目,在保证晶圆测试参数调整精度和覆盖率前提下,晶圆测试的时间的减少和测试成本的降低将是非常可观的。

5 结语

本文提出了一种晶圆级 ATC 测试理念并应用到先进混合信号芯片的大规模生产针测,同时提出了基本的 ATC 基本组成元素和实现算法。此算法在业界主流的测试平台上进行 CP 针测程式的开发和验证,参数调整的覆盖率和正确率在研发和生产过程中得到了良好反馈。

先进混合信号 SoC 芯片持续随着摩尔定律演进, 芯片的制造变异性对产品良率的影响越来越不可忽视。前端制造 APC 和晶圆针测 ATC 同时应用,对于先进工艺良率提升和可制造性的增强,将会发挥越来越大的作用。

-

晶圆

+关注

关注

52文章

5011浏览量

128526 -

APC

+关注

关注

0文章

36浏览量

11562 -

ATC

+关注

关注

0文章

29浏览量

11911

原文标题:ATC 在先进工艺晶圆测试中的应用

文章出处:【微信号:appic-cn,微信公众号:集成电路应用杂志】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

ATC2对定时和信号路由的影响

ATC2核心尺寸与资源

城轨交通ATC仿真系统的设计与实现

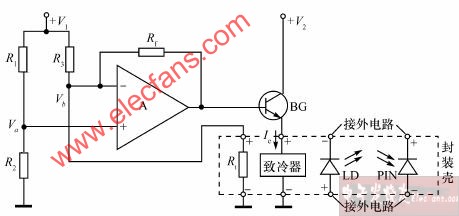

自动温度控制电路(ATC)

取数语言在ATC报表系统中的设计

MAX31730ATC+T MAX31730ATC+T - (Maxim Integrated) - 温度传感器 - 模拟和数字输出

MAX31730ATC+ MAX31730ATC+ - (Maxim Integrated) - 温度传感器 - 模拟和数字输出

MAX9517ATC+ MAX9517ATC+ - (Maxim Integrated) - 线性 - 视频处理

MAX9524ATC+ MAX9524ATC+ - (Maxim Integrated) - 线性 - 视频处理

MAX9517ATC+T MAX9517ATC+T - (Maxim Integrated) - 线性 - 视频处理

MAX9524ATC+T MAX9524ATC+T - (Maxim Integrated) - 线性 - 视频处理

MAX16000ATC+ PMIC - 监控器

MAX17610ATC+T PMIC - 电流调节和管理

ATC在工艺晶圆测试中的应用和理念及ATC基本组成元素和实现算法

ATC在工艺晶圆测试中的应用和理念及ATC基本组成元素和实现算法

评论