LV/HV P-Well BCD技术的芯片与制程剖面结构

LV/HV P-Well BCD技术能够实现低压 5 V 与高压 100~700 V(或更高)兼容的 BCD 工艺。为了便于高低压 MOS 器件兼容集成,采用源区为硼磷双扩散形成沟道的具有漂移区的偏置栅结构的 HV LDMOS 器件。改变漂移区的长度,宽度,结深度以及掺杂浓度等可以得到不同的高电压。采用 MOS 集成电路芯片结构设计﹑工艺与制造技术,依该技术得到了芯片制程结构。

1 制造技术的整合

LV/HV P-Well BCD[B] 制造工艺能够实现低压 5V 与高压 100~700 V 范围(或更高)兼容的工艺技术,即以 LV P-Well BiCMOS[B] 芯片与制程结构[1]为基础,引入源区作异型双扩散,在沟道和漏极之间具有场氧化层(F-Ox),形成适合于 HV 要求的漏漂移区的器件工艺,以制得 HV LDMOS 的兼容技术,实现同一硅衬底上形成 LV CMOS﹑LV 双极型以及 HV LDMOS 等器件,并使之互连,以实现 LV/HV 兼容 BCD 技术。改变漂移区的长度,宽度,结深度,掺杂浓度等可以得到不同的高压。实际上,把 HV LDMOS 器件引入 LV BiCMOS[B] 集成电路中,使之整合于一体。因此,制造工艺复杂,兼容了双极,CMOS,DMOS 的工艺技术。

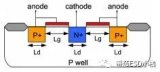

HV LDMOS 与偏置栅 MOS 结构相同点都是偏置栅,长的漂移区,而不同点 LDMOS 源区作异型双扩散,具有短的沟道,驱动能力大。

LV/HV 兼容 BCD 工艺有许多种,可以分成两类:一类 LV/HV P-Well BCD[C] 工艺技术[2];另一类以 LV BiCMOS[B] 工艺为基础,引入 HV LDMOS 工艺,以制得 HV LDMOS 的兼容技术,并以 LV/HV P-Well BCD[B] 来表示。这种技术可分成两种不同结构:HV LDMOS 和 HV VDMOS。现先叙述前一种结构。在 LV/HV P-Well BCD[B] 技术(1)芯片结构与制程中,采用 HV LDMOS 结构。

为了描绘出双极型与 CMOS/LDMOS 器件兼容集成的 LV/HV P-Well BCD[B] 技术(1)制程结构,本文应用芯片结构技术[2],可以得到芯片剖面结构。并利用计算机和它所提供的软件,可以得到芯片制程中各个工序剖面(或平面/剖面)结构。依照各个工序的先后次序互相连接起来,可以得到制程剖面(或平面/剖面)结构。该结构的示意图直观显示出 LV/HV P-Well BCD[B] 技术(1)制程中芯片表面﹑内部器件以及互连的形成过程和结构的变化。

2 芯片剖面结构

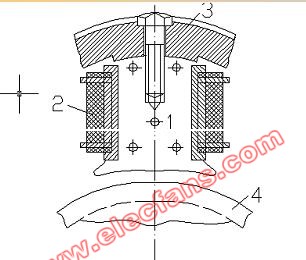

应用芯片结构技术[2],使用计算机和它所提供的软件,可以得到 LV/HV P-Well BCD[B]技术(1)芯片典型剖面结构。首先由设计人员在电路中找出各种典型元器件:LV NMOS,LV PMOS,LV NPN(纵向), LV PNP(横向)以及 HV LDNMOS。然后由制造人员对这些元器件进行剖面结构设计,选取剖面结构各层统一适当的尺寸和不同的标识,表示制程中各工艺完成后的层次,设计得到可以互相拼接得很好的各元器件结构(或在元器件结构库中选取),分别如图 1 [A]﹑[B]﹑[C]﹑[D]以及 [E] 所示(不要把它们看作连接在一起)。最后把各元器件结构依一定方式排列并拼接起来,构成芯片剖面结构,图 1A 为其示意图。以该结构为基础,消去 LV PNP,引入 Poly 电阻和场区电容,改变 NPN 结构,得到如图 1B 结构。如果引入不同于图 1 中的单个或多个元器件结构或对其中元器件结构进行改变,则可得到多种不同结构。选用其中与设计电路相联系的一种结构。下面仅对图 1A 结构作叙述。

3 工艺技术

电路采用 1.2 μm 设计规则,使用 LV/HV P-Well BCD[B]工艺技术(1)。该电路主要元器件﹑制造技术以及主要参数如表 1 所示。它以 LV P-Well BiCMOS[B] 制程及其所制得的元器件 [1] 为基础,引入兼容偏置栅 HV LDMOS 器件工艺,最终在同一硅衬底上形成高低压器件,并使之互连,实现所设计电路。该电路或各层版图己变换为缩小的各层平面和剖面结构图形的 IC 芯片。如果所得到的工艺与电学参数都适合于所设计电路的要求, 则芯片功能和电气性能都能达到设计指标。

表 1 中参数中:高-低压栅氧化层厚度为 THV-Gox/TLV-Gox,DP- 区结深,薄层电阻为 XjDP-/RSDP-,LDNMOS 有效沟道长度/漂移区长度为LeffLDN/LDLDN,导通电阻为 RON,其它参数符号与通常表示相同。

为实现 LV/HV P-Well BCD[B] 技术(1),引入 HV LDNMOS 器件工艺,对 LV P-Well BiCMOS[B] 工艺[1]作如下改变。

(1)N- 型外延层中 P-Well 推进后,引入 11B+ 注入并推进,生成 DP- 区,源漏掺杂后形成 N+/DP- 区为双扩散源,N+ 区为漏,沟道和漏之间适合于 HV 要求的长的低浓度的 N- 型外延层为漂移区。

(2)场区氧化后,在沟道与漏之间引入场氧化层,形成适合于 HV 要求的厚度和长度。

(3)腐蚀预栅氧化层后,引入厚﹑薄栅氧化膜生长。

(4)Poly 淀积并掺杂,引入刻蚀形成偏置栅结构。上述引入这些基本工艺,使 LV P-Well BiCMOS[B] 芯片结构和制程都发生了明显的变化。工艺完成后,以制得 LV NMOS 与 LV PMOS [A,B],LV NPN 和 LV PNP [C,D] 以及 HV LDNMOS,并用 LV/HV P-Well BCD [B] 技术(1)来表示。

P-Well BCD [B] 技术(1)电路电气性能/合格率与制造各种参数密切相关,确定用于芯片制造的基本参数,如表 1 所示。

(1)工艺参数:如各种掺杂浓度及其分布,XjBLN+/XjIP+/XjDN/XjPW/XjDP-/XjN+/XjP+ 等结深,TF-Ox/THV-Gox/TLV-Gox 等氧化层厚度以及 LDLDN 等。

(2)电学参数:ULV/UHV 等 LV/HV 阈值电压,RSBLN+/RSIP+/RSDN/RSPW/RSDP-/RSN+/RSP+ 等薄层电阻,BULVDSN/BULVDSP,BUCBO/BUCEO 等击穿电压,β以及 RON 等。

(3)硅衬底电阻率/外延层厚度及其电阻率等的要求,制定出各工序具体工艺条件,以保证所要求的各种参数都达到规范值,而且确保批量生产中电路具有高成品率,高性能以及高可靠性。

制作掩模时,通常设计者要与制造者一起来确定。如果应用芯片结构及其制程剖面结构技术,则不难确定出各次光刻工序及其所用掩模的名称﹑图形黑白﹑正胶﹑划片槽有无以及对准层次。

由下面制程剖面结构图 2 中可以看出光刻工序各个层次,需要进行 17 次光刻。因此,光刻对准曝光要严格对准﹑套准,并使之在确定的误差以内。与 LV P-Well BiCMOS[B] 相比,增加了 1块掩模:HV 栅氧化膜区,DP- 区是基区, 并兼作PNP 集电区轻掺杂区和双扩散源区。

4 工艺制程

图 1 所示的 LV/HV P-Well BCD[B] 技术(1)芯片结构的制程是由工艺规范确定的各个基本工序﹑相互关联以及将其按一定顺序组合构成。为实现此技术,在 LV BiCMOS 制程中引入上面的(1)~(4)的基本工艺,不仅增加了制造工艺,使芯片结构发生了明显的变化,而且改变了制程,从而实现了 LV/HV P-Well BCD[B] 技术(1)制程。

制程需要运行多次氧化﹑光刻﹑杂质扩散﹑离子注入﹑薄膜淀积以及溅射金属等主要工序。这些工序提供了以下工艺结构。

(1)形成电路芯片中的各个元器件:LV NMOS,LV PMOS,LV NPN(纵向),LV PNP(横向)以及 HV LDNMOS 等。

(2)这些电路元器件所需要的精确控制的硅中的杂质层:BLN+,N-EPI, IP+, DN, P-Well,DP-,PF,NF, 沟道掺杂,SN-,N+Poly,N+,P+ 等。

(3)形成集成电路所需要的介质层:F-Ox, LV/HV G-Ox,Poly-Ox,TEOS, BPSG/LTO 等。

(4)这些电路元器件连接起来形成集成电路所需要的金属层:AlSiCu。这些按给定的顺序进行的制造步骤构成了制程。

应用计算机,依据芯片制造工艺中的各个工序的先后次序,把各个工序互相连接起来,可以得到 LV/HV P-Well BCD[B] 技术(1)制程。该制程由各工序所组成,而工序则由各工步所组成来实现。根据设计电路的电气特性要求,选择工艺规范号和工艺序号,以便得到所需要的工艺和电学参数。

为了直观地显示出制程中芯片表面﹑内部元器件以及互连的形成过程和结构的变化,藉助图 1 芯片剖面结构和制造的各个工序,利用芯片结构技术,使用计算机和它所提供的软件,可以描绘出芯片制程中各个工序剖面结构,依照各个工序的先后次序互相连接起来,可以得到 LV/HV P-Well BCD[B] 技术(1)制程剖面结构,图 2 为其示意图。

(1)衬底材料 P-Si<100>,初始氧化(Init-Ox)(1),光刻 BLN+ 埋层, 腐蚀SiO2, BLN+ 区氧化(BLN+-Ox), 121Sb+注入,如图 2-1 所示。

(2)注入退火,BLN+ 区推进/氧化,腐蚀净 SiO2,N- 型外延(N-EPI),初始氧化(Init-Ox)(2),光刻隔离区(IP+),腐蚀SiO2, 隔离区氧化(IP+ -Ox),11B+ 注入,如图 2-2 所示。

(3)注入退火,隔离区(IP+)推进/氧化,光刻 DN 区,腐蚀 SiO2, DN 区氧化(DN-Ox),31P+ 注入,如图 2-3 示。

(4)注入退火,DN 区推进/氧化,光刻P-Well 区,腐蚀 SiO2, P-Well 区氧化(PW- Ox),11B+ 注入,如图 2-4。

(5)注入退火,P-Well 推进/氧化,光刻 DP- 区,腐蚀 SiO2, DP- 区氧化(DP- -Ox),11B+ 注入,如图 2-5 所示。

(6)注入退火,DP- 区推进/氧化,腐蚀净SiO2, 基底氧化(Pad-Ox),Si3N4 淀积,光刻有源区,刻蚀 Si3N4,如图 2-6示。

(7)光刻 P 场区(PF),11B+ 注入,如图 2-7 所示。

(8)光刻 N 场区(NF),31P+ 注入,如图2-8 所示。

(9)注入退火, 场区氧化(F-Ox)如图 2-10 。

(10)三层(SiON/Si3N4/SiO2)腐蚀,预栅氧化(Pre-Gox), 光刻 LV P 沟道区,11B+ 注入,如图 2-10 所示。

(11)腐蚀预栅氧化,注入退火,HV 栅氧化(HV-Gox),光刻 HV 栅氧化层,腐蚀 SiO2,LV 栅氧化(LV-Gox),如图 2-11 所示。

(12) Poly 淀积,POCl3 掺杂,光刻 Poly,刻蚀 Poly/SiO2,如图 2-12 所示。

(13)源漏氧化(S/D-Ox),光刻 NLDD 区,31P+ 注入(Poly 注入未标出),如图 2-13 所示。

(14)注入退火,形成 SN- 区,TEOS 淀积/致密,刻蚀形成 TEOS 侧墙,源漏氧化(S/D-Ox),如图 2-14 所示。

(15)光刻 N+ 区,75As+ 注入(Poly 注入未标出),如图 2-15 所示。

(16)光刻 P+ 区,49BF2+ 注入(Poly 注入未标出),如图 2-16 所示。

(17) LTO/BPSG 淀积,流动/注入退火,形成P+﹑N+SN- 区(图中未标出 SN-),光刻接触孔,腐蚀, 刻蚀 BPSG/LTO/SiO2,如图 2-17 所示。

(18)溅射金属(Metal),光刻金属, 刻蚀ALSiCu, 如图 2-19 所示。

LV/HV P-Well BCD[B]技术(1)制程的主要特点汇总如下。

(1)LV BiCMOS[B] 中的 LV NPN 基区和 LV PNP 集电区中的轻掺杂区的与 HV LDNMOS 双扩散源区中的 DP- 区都是同时形成,具有相同的结深和浓度。

(2)LV PNP 的发射区/集电区和 LV NPN 基区接触的 P+ 掺杂, 同时在 N- 外延层中形成源区和漏区,以制得 LV PMOS。

(3)LV NPN 的发射区/集电区和 LV PNP 的基区接触的 N+ 掺杂。① 同时在 P-Well 中形成源区和漏区, 以制得 LV NMOS。② 同时在 N- 外延层中 形成双扩散源区和漏区,且在沟道和漏区之间具有场氧化层(F-Ox),以制得 HV LDNMOS,而双扩散源区中的 DP- 区是在 N- 外延层中作 11B+ 注入形成的。

(4)LV BiCMOS[B] 中的栅氧化改变为厚栅氧化膜生长,使用增加一次掩模,并先作腐蚀,得到高压厚栅氧化膜。然后,接着氧化,以形成低压栅氧化膜。

5 结语

制程中使用了 17 次掩模,各次光刻确定了 LV/HV P-Well BCD[B] 技术(1)芯片各层平面结构与横向尺寸。工艺完成后确定了以下参数。

(1)芯片各层平面结构与横向尺寸。

(2)剖面结构与纵向尺寸。

(3)硅中的杂质浓度﹑分布及其结深。

(4)电路功能和电气性能等。

芯片结构及其尺寸和硅中杂质浓度及其结深是制程的关键。它们不仅与 HV 器件下列参数相关。

(1)HV LDNMOS N+/DP- 结深度﹑掺杂浓度和 N-EPI 漂移区的长度﹑结深度﹑掺杂浓度。

(2)HV DMOS 沟道和漏极之间形成场氧化层(F-Ox)厚度及其长度。

(3)HV 栅氧化层厚度。

(4)器件承受的高压﹑低的导通电阻以及阈值电压等有关。

而且与 LV 器件下列参数相关。

(1)CMOS 工艺参数(P-Well 深度及其薄层电阻,各介质层和栅氧化层厚度,有效沟道长度,源漏结深度及其薄层电阻等)及其电学参数(阈值电压,源漏击穿电压,以及跨导等)。

(2)双极型工艺参数(埋层/隔离/发射区的结深度及其薄层电阻,基区宽度及其薄层电阻,外延层电阻率及其厚度等)及其电学参数(fT﹑β﹑BUceo﹑以及 BUcbo 等)有关。这些参数如表1所示。CMOS 与双极型的这些参数之间必须进行折衷并优化,以达到互相匹配。

-

MOS

+关注

关注

32文章

1269浏览量

93683 -

BCD

+关注

关注

1文章

88浏览量

29714 -

LV

+关注

关注

0文章

10浏览量

28041 -

hv

+关注

关注

0文章

7浏览量

23728 -

集成电路芯片

+关注

关注

0文章

62浏览量

9503

原文标题:LV/HV P-Well BCD[B] 技术(1) 的芯片与制程剖面结构

文章出处:【微信号:appic-cn,微信公众号:集成电路应用杂志】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一文详解二极管在ESD防护中的应用

高性能的3bit串转并驱动芯片ZQ9712HV电子资料

求分享实现一些十进制到BCD和BCD到十进制的子例程

灰度高压驱动芯片HV632的结构原理

亚微米BiCMOS[B]芯片及其剖面结构与制程技术分享

CMOS工艺制程技术的详细资料说明

微机原理与接口技术教程之8086系统结构的资料概述

LV5683P LDO稳压器 4通道

LV5696P 线性稳压器 6通道 带高侧开关

HV-CMOS工艺制程技术简介

LV HV P-Well BCD技术的芯片与制程剖面结构的资料概述

LV HV P-Well BCD技术的芯片与制程剖面结构的资料概述

评论