智能手机和可穿戴电子设备等手持和便携式无线产品依赖可置入设备的微型芯片、贴片和印制线天线。尽管这些小型器件解决了在小尺寸系统中携带多频带天线阵列的问题,但它们也引入了辐射效率下降、阻抗匹配以及与附近物体和人体的交互等相关问题。

为解决这些问题,设计人员开始采用新的设计和电路方法,让这些天线不只成为一个独立的元器件,而是成为能够化解上述诸多设计挑战的动态天线子系统的一部分。这一设计转变需要进行大量仿真和分析,而不断改进的场解算器软件可以满足这一需求。

芯片、贴片天线提供了折衷之选

从传统的外部鞭形或短截天线过渡至芯片和贴片天线的原因很多,首当其冲的是外部天线存在的美观性和易折性问题。从性能的角度而言,智能手机等设备在给定的频带往往需要多个天线才能提供天线分集,进而改善性能。此外,多频带设备(尤其是与新兴的 5G 标准兼容的设备)在其必须支持的每个频带,都需要单独的独立式天线。尽管有这么多原因,但芯片和贴片天线也有自身的短板。

芯片天线使用多层陶瓷结构构成在目标频率谐振的元器件(图 1)。与其他所有表面贴装元器件一样,它们的尺寸很小,可以轻松地贴装在 PC 板上。

图 1:没有体积小、成本低且易于应用的陶瓷芯片天线,许多便携式无线设备将无从实现。图中显示的是 Johanson Technology 2450AT18B100E,位于广泛使用的 2.4 至 2.5 GHz 频段的中间位置。(图片来源:Johanson Technology)

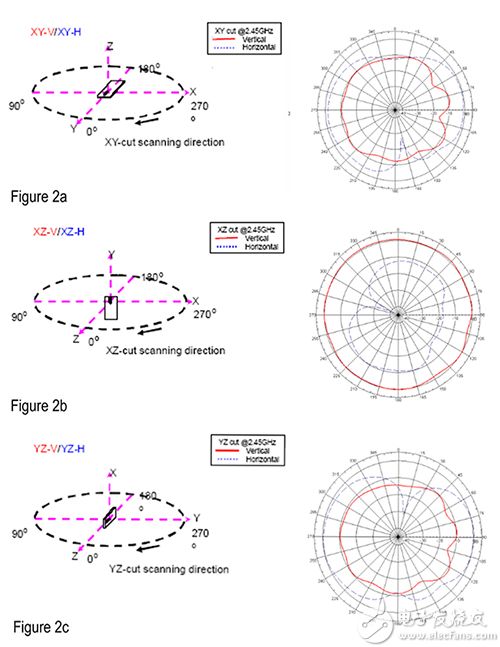

我们用两个例子来说明它们的特性。Johanson Technology 2450AT18B100E 是适用于 2.4 至 2.5 千兆赫 (GHz) 频段的 1.6 x 3.2 mm 芯片天线,尽管它的体积很小,却能提供近乎全向的辐射模式,而无需考虑方向(图 2)。类似这样的天线在便携式和手持无线设备中已得到广泛的成功应用。尽管芯片天线自身很简单,但设计人员必须将相关的驱动器电路与其 50 Ω 标准阻抗相匹配。当在分集架构中使用多个芯片天线时,这可能成为一大难题。

图 2:Johanson 描述了芯片天线在全部三个轴(自上而下分别为:a) XY、b) XZ 和 c) YZ)上的辐射模式;请注意,该模式在所有三个轴上近乎全向。(图片来源:Johanson Technology)

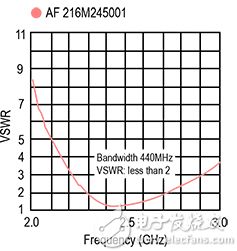

另一款芯片天线是 Taiyo Yuden AF216M245001-T,用于仿真同样适合 2.4 至 2.5 GHz 频带的单极螺旋形天线。该天线的尺寸为 2.5 x 1.6 mm,同样具有近乎全向的特征,并且可在 2.45 GHz 至 2.7 GHz 频带保持低于 2:1 的 VSWR(图 3)。

图 3:Taiyo Yuden 的 AF216M245001-T 芯片天线可在其主要工作带宽 2.45 GHz 至 2.7 GHz 范围内保持 2:1 的 VSWR。(图片来源:Taiyo Yuden)

由于芯片天线具有成本低、体积小和易于使用等特点,它们看起来是可满足众多无线需求的最优解决方案。尽管很多情况下的确如此,但在现实中,与所有元器件一样,芯片天线也有自己的短板。在此案例中,它们的典型效率相对较低,仅为 40% 至 50%,而且容易受周边的固定和变化条件影响,包括 PC 板布局、附近的元器件和用户等。

芯片天线的替代产品是贴片天线(图 4)。尽管它的尺寸比芯片设计要大,但相当扁平,因此往往能够沿产品外壳的内侧放置,远离元器件和其他辐射模式失真源。

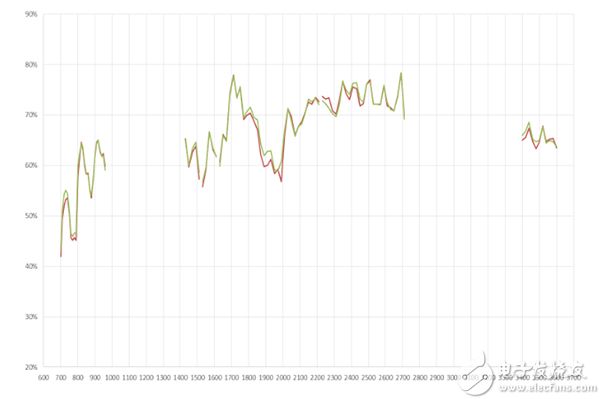

贴片天线(例如 Pulse Electronics 的 W6112B0100)可支持包括智能电表、远程监测和物联网设计在内的 2 x 2 多路输入、多路输出 (MIMO) LTE 应用。尽管该天线的尺寸大于芯片天线(约为 8.8 英寸长 × 0.8 英寸高),但根据所支持的具体频带,其效率可达 55% 至 75%(图 5)。

图 4:贴片天线(例如 Pulse Electronics 的多频带 W6112B0100)并非贴装在 PC 板上,而是连接到产品外壳的内部,远离板和电路。(图片来源:Pulse Electronics)

图 5:适用于 2 x 2 MIMO 4G/LTE 的 W6112B0100 设计为在 698 MHz 至 960 MHz、1.428 GHz 至 1.51 GHz、1.559 GHz 至 1.61 GHz、1.695 GHz 至 2.2 GHz、2.3 GHz 至 2.7 GHz 和 3.4 GHz 至 3.6 GHz 等多个频带工作,并能保持较高的效率。(图片来源:Pulse Electronics)

第三种天线选择是 PC 板印制线方法,该方法使用 PC 板的一个或多个蚀刻层来创建天线。此解决方案没有直接的 BOM 成本,并且极度灵活,因为它能用于创建使用分立元器件无法实现的定制或独特天线。单一的印制线天线可以覆盖包括滤波在内的多个频带,并且支持多极化。

但天下没有“免费的午餐”,因为印制线天线往往需要占用大量的 PC 板空间,而且它的性能会受附近布局、元器件贴装和元器件类型的很大影响。理论上的印制线天线与其实际安装之间存在可能很难逾越的重大差距。

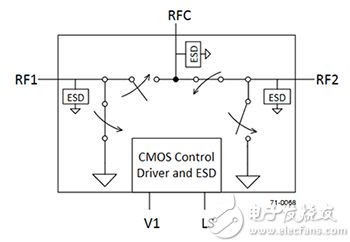

当系统包含多个天线,而拓扑要求在天线之间切换时,就会出现这样的问题——如何实现切换。机电开关很有效,并且具有出色的电气规格,但对于小型或便携式设备以及需要快速开关的设备而言,这显然不切实际。相反,应使用电子开关,通常是基于 PIN 二极管的开关(参见“射频开关如何以及为何使用 PIN 二极管”)或固态开关(参见“半导体射频开关:体积小但性能强的电路元器件”)。尽管有时需要 PIN 二极管的属性,但与基于 PIN 二极管的开关相比,固态开关更容易使用和引入到电路设计中。

例如,Peregrine Semiconductor 的 PE42422MLAA-Z 是一款不含任何移动零件的基本 SPDT 射频开关,适合在 5 MHz 至 6 GHz 频带工作。将其引入到电路设计时,面临的设计挑战也较少(图 6)。这款 50 Ω 元器件采用微型 12 引线 2 x 2 mm QFN 封装,结合了板载的 CMOS 控制逻辑和低压 CMOS 兼容型控制接口,无需外部元器件。它通常能在 2 毫秒内完成通道切换。

图 6:当有多个天线时,往往需要在天线之间切换射频信号路径。纯电子射频 SPDT 开关(例如 Peregrine Semiconductor 的 PE42422MLAA-Z)提供的方法只需通过简单的安装和控制便能做到这一点,而且在 5 MHz 至 6 GHz 频带范围的开关时间仅为 2 毫秒。(图片来源:Peregrine Semiconductor)

插入损耗的范围为 0.23 dB (100 MHz) 至 0.9 dB (6 GHz),整个范围内的三阶交调点 (IIP3) 为 75 dBm(最小值)。利用这类开关,可以轻松地在通用端口与两个独立端口之间实现隔离度为 68 dB(较低频率下)至 17 dB(较高频率下)的射频信号双向路由。插入损耗为 0.23 至 1.25 dB,同样取决于频率。

采用先进的技术解决现实世界的问题

任何天线的性能都会受到其周边环境的影响,包括附近的元器件、屏蔽和封装等。可以对这些元素的效应进行建模,并在最终设计中加以考虑,但这往往需要多次交互才能达到需求冲突的平衡(参见“了解天线的规格和操作,第 1 部分”和“了解天线的规格和操作,第 2 部分”。

但对于紧凑的便携式和手持设备,问题要复杂得多,因为天线的周边环境一直在变化。用户在使用时可能朝不同的方向或靠近身体的不同部位(手腕、头部或躯干)握持产品,或将产品放在其他物体的附近。因此,天线处于次优环境中,在此环境中,天线的有效阻抗和共振频率会发生变化并导致性能下降。

当天线的共振频率发生偏移时,其呈现给无线电前端剩余部分的阻抗也会偏离初始值,造成阻抗失配。阻抗失配会产生三种效应。更多的能量从天线端子反射回来,而不是通过这些端子;由于负载牵引的原因,来自功率放大器 (PA) 的输出功率下降;以及天线的辐射效率由于容性负载而降低。

过去几十年里,天线面临的这一处境导致射频链路预算不断下降,从而影响了产品的性能。由于网络和系统级性能的提升,这一性能降级没有引起用户的注意。更多的蜂窝基站、蜂窝基站天线波束形成的使用以及改进的误差校正技术,在很大程度上对其进行了补偿。由于系统级需求和用户需求不断提高,尤其对于新兴的 5G 标准,这类补偿可能已经“入不敷出”了。

与此情形相关的损耗模式有三种:吸收损耗、阻抗失配损耗和天线辐射效率损耗。吸收损耗可能高达 8 到 10 dB,并且目前为止我们对此无能为力。阻抗失配损耗约为 1 到 2 dB,而天线辐射效率损耗约为 2 到 3 dB。可通过两种方法来弥补阻抗失配和辐射效率损耗:更改天线的匹配电路和更改天线的谐振。

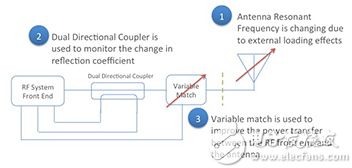

无线设备供应商在其最新一代的设备中已经解决了该问题。动态调谐可以补偿导致天线共振频率发生偏移的头部和手部效应。这是通过使用闭环调谐周期减少天线与功率放大器 (PA) 之间的失配以优化功率传输来实现的(图 7)。

图 7:闭环调谐用于动态修改阻抗匹配网络以实现最优性能及减少损耗。(图片来源:Antennasonline.com)

在闭环调谐中,将会实时检测不可避免的反射系数变化。方法是通过定向耦合器同时监测天线端子上的正向功率和反射功率的幅度和相位(参见“微型定向耦合器可满足紧凑型射频应用的需求”)。然后,系统将合成一个用于调整位于天线馈电点的匹配网络的复数共轭,以增强前端与天线之间的射频功率传输。这可以将损耗减少多达 1 到 3 dB。

这种闭环调谐方法尽管很有用,但也存在几点不足。测量反射系数的幅度和相位,然后确定共轭匹配,这需要大量的计算周期和时间,或者需要使用查询表。查询表的速度较快,但精度较低。为实施复杂的匹配,需要采用复杂的匹配电路。使用此方法实现的性能提升通常为 1 到 3 dB。

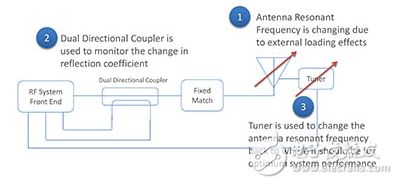

闭环调谐的替代方法是孔调谐,该方法通常与阻抗匹配搭配使用。这种情况下,将以电气方法更改天线尺寸(调谐状态),将其谐振恢复到最大功率传输点,而不是调整匹配网络以适应天线阻抗变化(图 8)。这需要大量小间距的调谐状态。

图 8.经过孔调谐的天线会动态调整天线的谐振长度以最大限度减少损耗。(图片来源:Antennasonline.com)

这种情况下,与闭环调谐一样,将在天线的馈电端子处测量反射系数。接着,使用其中的一种方法执行此测量,确定最佳的新调谐状态。其中三种方法为标量方法,只需使用简单的定向耦合器监测天线端子处的反射功率幅度,然后应用不同的计算方法(被称为平方拟合、阈值调整或凹点检测)。

第四种方法基于矢量,并使用反射系数的幅度和相位来确定天线结构的 S 参数矩阵解,然后确定恢复天线的共振频率所需的调谐器设置。通常可减少 2 到 4 dB 的损耗。与阻抗匹配结合使用,总体改进范围为 3 到 7 dB。

对设计成败至关重要的建模和仿真

对于标准鞭形设计等外部天线,在设计周期的早期只有极少甚至不进行任何性能建模。但对于芯片、PC 板印制线天线,甚至对于非常靠近低噪声放大器或功率放大器的贴片天线而言,天线仿真及其实现都至关重要。不可能仅通过构建、测试、修改、重复和迭代就能找到合适的配置。不仅必须对天线进行建模,还必须对整个周边环境(PC 板、元器件、外壳甚至用户的手或头部位置)进行建模和分析。

所幸的是,已经有很多先进的电磁场解算器应用程序包能够解决仿真问题。为其提供支持的是功能强大的 PC 或基于云的计算平台,它们能够运行这些场解算器执行分析所需的海量计算。这些场解算器还能通过最小值/最大值试验或跨多个变量的蒙特卡罗运行,来分析设计容差的影响。它们可以显示在 GHz 频率下即便几分之一毫米的变化也能产生重大影响,实施“假设”分析以研究可能的设计变更产生的影响,以及突显设计的不足或意外的特征。

总结

尽管天线的功能很简单,但它是将电路中的电功率转换为电磁场以及执行反向转换的复杂电磁传感器。传统的单元件天线(例如偶极和鞭形天线)现已增强为使用多层陶瓷、扁平贴片结构甚至产品自身的 PC 板的一个或多个天线。

将这些天线结合到紧凑型(通常为便携式)产品,需要仔细分析整个系统和封装,验证天线的理想化性能未受到过大的影响,并且能够达成设计目标。利用场解算器软件可以做到这一点,这类软件能够为实际安装中的电磁场和天线性能的详细建模及相关计算提供有力的支持。

-

智能手机

+关注

关注

66文章

18565浏览量

181357 -

贴片天线

+关注

关注

3文章

31浏览量

20179 -

可穿戴设备

+关注

关注

55文章

3825浏览量

167416

发布评论请先 登录

相关推荐

为何IBIS建模对设计成功至关重要

新一代小区网关:灵活性与高性能至关重要

为什么DSP对音频设计至关重要?

天线系统在NFC设备中至关重要

线程如何与CPU工作,为什么对系统性能至关重要

为什么说电源和电源轨至关重要?资料下载

为什么说LED电源的来料检验至关重要

选择合适的无线技术至关重要

IBIS建模:为何IBIS建模对设计成功至关重要

为何说设计成败至关重要是建模和仿真

为何说设计成败至关重要是建模和仿真

评论