一个总线周期由多个不可分的时钟周期构成,完成单次读/写操作、块读/写操作或者读改写操作。总线周期也分为单次读/写周期、块读/写周期和读改写周期。一次块读/写总线周期完成多次数据读/写操作。一般情况下,一次操作由主设备和从设备控制信号间的一次握手,以及同时进行的地址和数据总线的一次传输构成。块操作表示整个操作需要完成多次数据传送。在总线周期中主设备和从设备预先设定好的共同遵守控制信号握手规则,以及地址和数据总线的传输规则称作总线协议。

在下文(包括以后的博文中)所给图例中给出的信号均为主设备的输入输出信号。因此,对操作的描述也从主设备信号的角度展开,以便于读者对照正文理解图例。比如"在时钟上升沿1到达之前,从设备检测到主设备发起的操作,将适当的数据放到主设备的输入信号DAT_I()和TGD_I(),将主设备的ACK_I置高作为对主设备STB_O的响应。"的等价描述为:"在时钟上升沿1到达之前,从设备检测到主设备发起的操作,将适当的数据放到其输出信号DAT_O()和TGD_O(),将输出信号ACK_O置高作为对主设备STB_O的响应。"

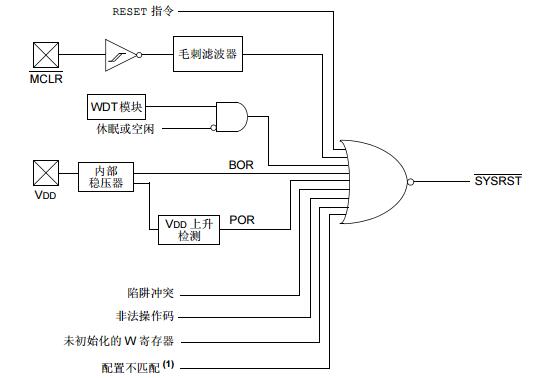

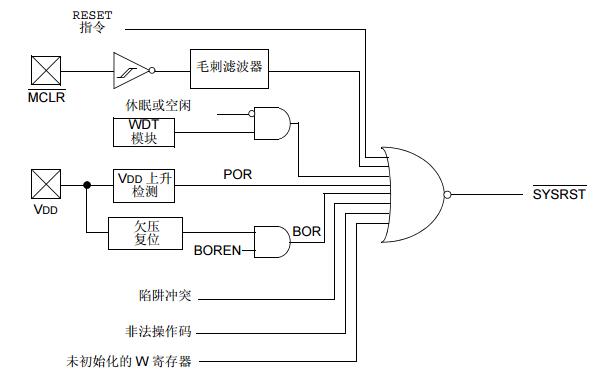

复位操作

复位是数字系统最基本的操作。复位后,系统进入预定的状态。在遵守Wishbone总线规范的系统中,当RST_I信号有效,系统开始复位。由于Wishbone规范规定的复位是同步复位,因此在复位信号有效后接下来的时钟上升沿,所有信号和寄存器进入预定状态。因此,Wishbone规范要求RST_I信号有效时间至少要一个时钟周期。在数字系统中,实际上更多的采用的是异步复位,而且复位信号的长度一般大于系统电平稳定时间和系统时钟频率稳定时间。如果在Wishbone接口中使用的是异步复位,设计者需要在文档中说明,因为Wishbone接口默认的是同步复位。

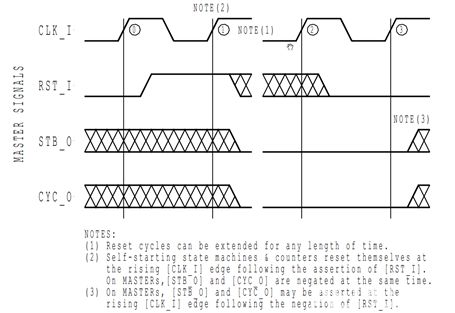

图6 Wishbone总线的复位操作

在图6中,我们只给出了STB_O和CYC_O这两个信号,而没有给出其它信号。当这两个信号无效时,所有其他信号没有意义。

规则3.00:所有的Wishbone接口必须在RST_I置位(变为1)后的第一个时钟上升沿进入初始化状态,直到RST_I被复位(变为0)后的第一个时钟上升沿到来。

规则3.05:RST_I必须被置位至少一个完整的时钟周期,才能有效地完成复位。

允许3.00:当然,RST_I也可以被置位多个时钟周期,但是数量必须是有限的。

规则3.10:所有的Wishbone接口必须能够在任意时间响应RST_I信号(优先级足够高)。

规则3.15:所有的Wishbone自启动状态机核计数器必须在RST_I置位(变为1)后的第一个时钟上升沿进入初始化状态,直到RST_I被复位(变为0)后的第一个时钟上升沿到来。

规则3.20:以下主机信号必须在RST_I置位(变为1)后的第一个时钟上升沿复位(变为0),直到RST_I被复位(变为0)后的第一个时钟上升沿到来:STB_O,CYC_O。所有的其他主机此时不能操作这些信号,以响应复位周期。RST_I被复位(变为0)后的第一个时钟上升沿到来后,主机接口的STB_O和CYC_O信号可以被立即置位(变为1)。

注意3.10:在标准模式下(除了流水线之外的模式),当STB_I被复位(变为0)时,从机接口应自动将ACK_O,ERR_O和RTY_O置位。

推荐3.00:设计SYSCON模块时,应保证上电复位时将RST_O信号置位。并且RST_O信号应该保持置位状态,直到电压和时钟频率进入稳定状态。最好使用同步复位的方式,以保证设计的兼容性。

注意3.15:在使用门控时钟的情况下,如果时钟被禁止了。此时,Wishbone总线将不能响应RST_I信号。

建议3.00:如果一些IP核或者SoC模块需要异步复位,应当将复位信号定义为非Wishbone标准信号。这样可以保证Wishbone接口使用纯同步时序,以避免造成疑惑。

注意3.20:所有的Wishbone接口信号都应能响应复位信号,除了IP核接口。

传输周期初始化

主机接口通过置位CYC_O信号进行初始化传输周期,当CYC_O信号被复位,其他所有的主机信号都被视为无效。从机也只在其CYC_I信号被置位的情况下,才会响应其他主机信号。应当注意,SYSCON信号不受影响。

规则3.25:在单独写周期、块读写周期和读改写周期(RMW)持续期间。主机接口必须将CYC_O信号置位。CYC_O信号置位时间必须不晚于STB_O置位后的第一个时钟上升沿,CYC_O信号置位时间必须不早于STB_O复位后的第一个时钟上升沿。

允许3.05:主机接口可以在任意时间置位CYC_O。

推荐3.05:仲裁逻辑经常使用CYC_I信号进行主机选择。保持CYC_O一直长时间处于置位状态可能会导致仲裁错误。因此在多主机情况下,应当避免使用【允许3.05】。

规则3.30:当CYC_I被复位时,从机接口可以不响应任何其他主机信号。但是其必须响应SYSCON信号。

-

信号

+关注

关注

12文章

2938浏览量

80432 -

总线

+关注

关注

10文章

3062浏览量

91906 -

Wishbone

+关注

关注

0文章

16浏览量

10615

原文标题:【博文连载】Wishbone总线周期之复位操作

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

e203接口ICB转wishbone,怎么操作?

wishbone总线

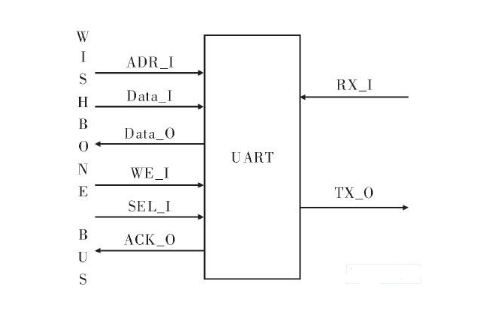

基于WISHBONE总线的FLASH闪存接口设计

基于Wishbone片上总线的IP核的互联

基于Wishbone总线的UART IP核设计

基于WISHBONE总线的FLASH闪存接口设计

基于WISHBONE总线的通用接口控制器

基于FPGA的SDX总线与Wishbone总线接口设计

Wishbone总线的异步周期结束路径

Wishbone总线的主要特征概括

Wishbone总线周期之复位操作

Wishbone总线周期之复位操作

评论