握手发生在主设备和从设备之间。握手协议是主设备和从设备在握手时所遵守的共同规则。除了,B3版中的标准模式之外,B4版的Wishbone官方手册中还新增了流水线模式。下面将依次进行介绍。

标准Wishbone协议

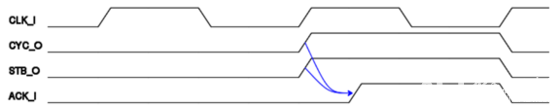

如图7所示,当主机准备传输数据时,应将STB_O置位,直到从机将以下任一信号(周期结束信号)置位:ACK_I、ERR_I或者RTY_I。在每一个时钟(CLK_I)上升沿,系统都会对周期结束信号进行采样。当任一周期结束信号被置位时,STB_O信号就会被复位。这就让主机和从机接口都有机会来控制数据的传输速率。

图7 标准总线握手协议,异步从机

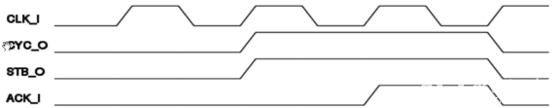

图8 标准总线握手协议,同步从机

允许3.10:在标准模式下,如果从设备保证能够在主设备发起操作时及时做出操作成功的响应,此时ERR_I和RTY_I信号可以不使用,ACK_O信号可以设计为STB_I和CYC_I信号的逻辑与。因此ERR_O和RTY_O信号是可选的,而ACK_O信号是必须的。在点对点连接中,甚至可以将ACK_I信号直接置高。当存在ERR_O和RTY_O信号,主设备当发现ERR_O和RTY_O信号之一有效时如何进行响应取决于主设备的设计。

注意3.25:在标准模式下,从机接口会置位一个周期结束信号来响应STB_I。然而,STB_I信号只有在CYC_I信号有效地时候才有效。

注意3.30:在总线周期期间置位ERR_I信号,会立即结束该周期,意味着从机通知主机在该周期期间发生了错误。当从机逻辑电路检测到错误,便会置位ERR_I信号。例如,如果从机使用了奇偶校检,当发生错误时,从机便会通过ERR_I做出反应。

在总线周期期间置位RTY_I信号,也会立即结束该周期,意味着从机通知主机在该周期期间发生了故障(Aborted)。该信号一般用于共享内存或者总线桥接。当本地资源处于忙状态时,从机电路便会置位RTY_I信号。应当注意,Wishbone规范并未强制要求主机何时对RTY_I信号做出相应。

规则3.40:实际上,对于主设备,其最小配置为ACK_I、CLK_I、CYC_O、RST_I和STB_O。所有的其他信号都是可选的(optional)。

允许3.20:主机和从机接口之间可以被设计成支持ERR_I/ERR_O信号。但是Wishbone规范并未要求主机对ERR_I信号做出什么响应,用于可以根据自己的需求设计。

允许3.25:主机和从机接口之间可以被设计成支持TRY_I/TRY_O信号。但是Wishbone规范并未要求主机对TRY_I信号做出什么响应,用于可以根据自己的需求设计。

规则3.45:当从机支持ERR_O和TRY_O信号时,应保证从机同一时刻只能将三个周期结束信号的其中之一置位。

注意3.35:如果从机支持了ERR_O和RTY_O信号,而主机不支持这些信号,可能会造成系统的死锁。

推荐3.10:通过设计INTERCON模块可以阻止死锁的情况发生。其中一种解决方法就是,设计一个看门狗定时器用来监控STB_O信号。当ERR_I或者RTY_I信号周期技术超出了预定义的限制时,INTERCON模块可以被设计成将Wishbone总线连接断开。

推荐3.15:在图7中,从STB_O到ACK_I存在一个长组合逻辑路径,在实际系统中很可能成为关键路径。因此,在设计中应尽量保证STB_O是触发器的直接输出。如果从STB_O到ACK_I存在一个长组合逻辑路径延迟不能满足设计的时序要求,可将从设备的ACK_O经过触发器寄存后再输出,从而将长组合逻辑打破,但系统的吞吐量也将因此减小。

规则3.50:从机接口必须被设计成ACK_O、ERR_O和RTY_O信号的置位或复位与STB_I信号的置位或复位有关。

允许3.30:ACK_O、ERR_O和RTY_O信号的置位允许被设计成异步逻辑(例如,STB_I与ACK_O之间的组合逻辑路径)。

注意3.40:ACK_O、ERR_O和RTY_O信号的异步置位可以保证每一个时钟周期可以完成一次数据传输。进一步来说,可以简化多主机情况下的仲裁器设计。

注意3.45:在某些场合,ACK_O、ERR_O和RTY_O信号的异步置位可能不能实现。例如,从机等待状态早于用寄存器实现的ACK_O信号。

注意3.50:在部分高速设计场合,ACK_O、ERR_O和RTY_O信号的异步置位可能会导致不可接受的延时时间,一般是由于主机和从机之间的回路延时导致的。使用寄存器实现ACK_O、ERR_O和RTY_O信号可以显著地减少这种回路延时。

允许3.35:在特定情况下,从机接口可能被设计成保持ACK_O信号一直处于置位状态。例如,一个单从机,单主机,点对点的接口,从机操作根本不需要等待时间。

规则3.55:当从机接口保持ACK_I信号为置位状态时,主机接口应当被设计为正常操作模式。

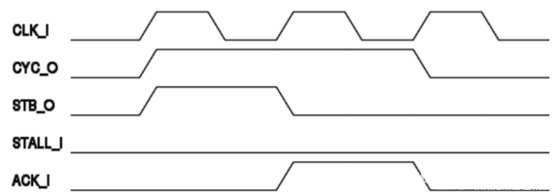

流水线Wishbone协议

在流水线模式下,握手协议主要有以下差异:

·主机在输出下一个地址/数据 字到总线上之前,不能等待ACK_I信号;

·主机接口上的STALL_I信号用于表示从机流水线此时可以接受另一个请求。总线仲裁器应该选择目标从机STALL_O信号,并将其告知主机。这种路径应当被设计成非寄存式的(non-registered)。

·主机当STALL_I信号为低电平时,输出请求。当STALL_I信号被置位时,则处于等待状态。即,当STALL_I信号被置位,流水线不能够产生任何请求。

·如果总线周期由N个转换构成,则最后一个ACK_I表示转换的终止。当接收到最后的ACK_I脉冲后,主机结束总线周期。

·只有当ACK_I信号为高电平时,读取数据操作才是有效的。

图9 流水线模式 单次访问

规则3.57:在流水线模式下,当CYC_I和STB_I信号被置位后,紧接着STALL_I和WE_I信号被复位时,一个读转换操作开始。

规则3.58:在流水线模式下,当CYC_I、STB_I和WE_I信号被置位后,紧接着STALL_I信号被复位时,一个写转换操作开始。

规则3.59:在流水线模式下,完成转换初始化后,主机必须能在任意时间接受ACK_I信号。

-

信号

+关注

关注

11文章

2811浏览量

77197 -

总线

+关注

关注

10文章

2909浏览量

88499 -

Wishbone

+关注

关注

0文章

16浏览量

10448

原文标题:【博文连载】Wishbone总线周期之握手协议

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

周期精确的流水线仿真模型

基于WISHBONE总线的FLASH闪存接口设计

采用单通道通讯协议设计高速异步流水线控制器STFB电路的设计

FPGA之为什么要进行流水线的设计

滚筒输流水线故障排除方法

如何选择合适的LED生产流水线输送方式

嵌入式_流水线

标准Wishbone协议:流水线Wishbone协议

标准Wishbone协议:流水线Wishbone协议

评论