经过上两篇文章的阅读,大家应该清楚自己的CPU大致是如何处理数据的,而又是如何执行指令的。我们现在来在简略的说一下流水线CPU的设计。(源码在CSDN下载页,请自取)

流水线CPU的基本数据通路和单周期没有什么太大区别,而且也是每个时钟周期都有一条指令执行结束。但是他又和多周期CPU一样一条指令需要多个时钟周期完成。而同时使这两条条件同时满足的就是流水线技术了。先上一张图

由于在多周期CPU中,比如我们正在第三级执行第五条指令的执行操作,对于整个数据通路来讲,其它几级都是空闲状态,那我们为了提高CPU的工作效率,就让他提前后边指令的其他几级操作。这样一来,我们的CPU就像工厂内的流水线一样,每一级都在工作,大大提升了他的工作效率。

在设计中,流水线CPU甚至会比多周期CPU更好实现。由于数据是一级一级向下流,我们都无需进行状态机的状态转移来控制,只需要让数据与他的控制信号同步流向器件。每一个时钟周期数据都是从上一级流向下一级。而对应的寄存器就是在每个时钟上升沿都读出旧数据,写入新数据。

但是在流水线CPU中,分支跳转语句变成了一个难点,当指令发现是分支跳转指令时,输出branch信号,后等待ALU输出比较值是否相等。如果相等,进行跳转。但是跳转时,我们的流水线已将后三条指令读入并操作了一部分了。这时我们便需要清空存储器。或者我们也可以当检测到branch信号时CPU停止读入指令,直到判断结果输出时在进行跳转。、

流水线CPU是非常好用的CPU,在我们后续的程序编写的时候基本上都会使用流水线CPU,偶尔也会用多周期CPU。

-

FPGA

+关注

关注

1629文章

21729浏览量

602978

发布评论请先 登录

相关推荐

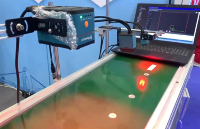

工业读码器解决方案在自动化流水线上扫描条码的应用

SMT流水线布局优化技巧

行云流水线 满足你对工作流编排的一切幻想~skr

ADS5413 CMOS流水线模数转换器(ADC)数据表

固定式的扫码器在SMT流水线中的使用

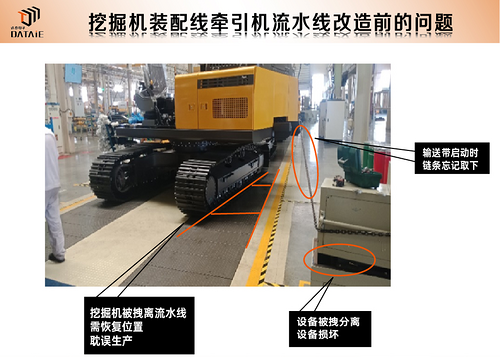

牵引机和挖掘机装配流水线自动互锁防呆系统无线通讯应用

自制CPU(三)流水线

自制CPU(三)流水线

评论