DDR5

在预计将于今年夏季发布的DDR5标准中,DRAM将被指定涵盖DFE(判决反馈均衡)能力。 而在实践中,DFE建模就意味着创建和使用AMI模型。 实际上,近十年来用于分析串行链路的技术正在扩展应用到并行存储器接口领域。

然而,SerDes和DRAM在本质上存在着一些差异。 串行链路通常很长且有损耗,而DRAM则较短且损耗较少。 低损耗貌似值得称赞,在某些方面它确实如此,但是反射会在低损耗链路中持续长时间的反弹,而在较长的串行链路中则由于高损耗而迅速衰减。 这就是DRAM需要使用DFE的原因:DFE会消除错误并解决反射问题。 SerDes中仅有一个发射器和一个接收器; 但是像PC和服务器这样的系统通常在同一条总线上有多个DIMM,有时还会有未插入的插槽,以上这些都会使反射问题变得更加棘手。

虽然JEDEC尚未最终完成DDR5标准,但是不论是我们的知识产权设计团队、DRAM供应商,还是我们在全力开发新一代信号完整性(SI)方案的Sigrity产品线团队,都不希望耗时在等待上。 开发进展刻不容缓,我们需要及时地做出必要的改变和调整,以在最终标准出台时满足用户要求。

AMI Builder

AMI Builder的目标是使用户能够从已知、良好的AMI模块库中快速构建符合IBIS的AMI模型,而不是从头开始在空白文本编辑器上费力编写容易出错的代码。 如果用户不具备类似C语言的良好的软件开发专业知识,那么应用难度无疑会陡然增加。

AMI Builder的基本方法是为发射器配置诸如FFE(前馈均衡)等构件。然后向导器会令用户对参数进行设置,某些情况下也会对参数进行自动计算。 例如,上图显示的是为FFE设置参数,然后令其计算抽头值。 图表可以直接从向导器中绘制,而无需执行仿真。

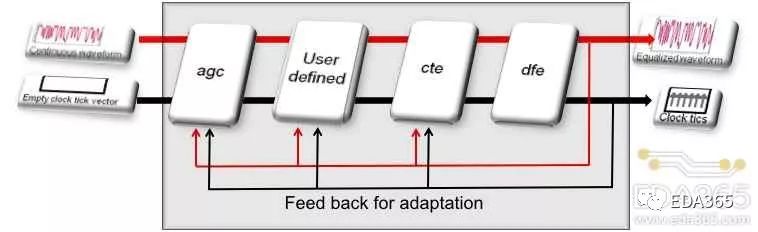

接收器路径如上图所示。AGC表示自动增益控制,CTE(或CTLE)是连续时间(线性)均衡器,DFE代表判决反馈均衡。 信号从通道左侧进入,在右侧则输出数据和已恢复的时钟。

一旦在向导器中设置好选项,模型就会立即被编译成DLL并可进行仿真和测试。在测试过程中,模块可以根据需要被启用、禁用、编辑或删除。该流程的一大优势是可以令用户专注于架构而无需费心编码,同时为用户提供轻松迅捷地按钮式模型创建方式。

AMI建模和AMI Builder技术最初为SerDes应用程序而开发,现已扩展到DDR应用领域。

针对DDR4的AMI

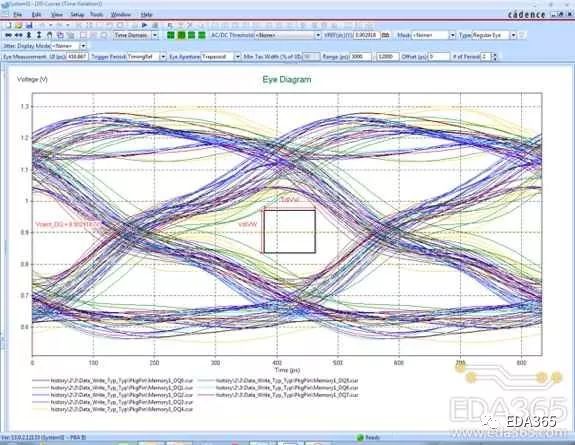

DDR4已经带来了一些新挑战,特别是DQ掩膜一致性检查。该功能可确保眼睛保持在掩膜之外,从而保证系统正常工作。 如上图所示,掩膜是中间的矩形框,而信号则成功地围绕其周,这意味着眼睛已睁开到足以符合标准的程度。

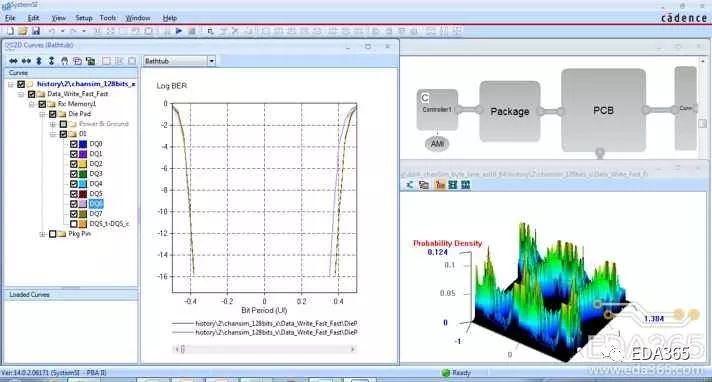

误码率(BER)分析也必不可少,因此我们需要通道仿真和浴盆曲线。 这里的浴盆曲线和与其同名的可靠性浴盆曲线毫无关系,后者用于在半导体使用寿命的开始和结束时显示高故障率(即早期故障期和后期老化期)。信号完整性浴盆曲线是通过给输入信号添加抖动和噪声来得到的。上图的中心窗格即显示浴盆曲线。其中有两个浴盆,一个是使用抖动来获得水平的(时间角度)浴盆,另一个则是使用噪声来获得垂直的(信号角度)浴盆。

由于需要的比特数量极大(数十万甚至数百万),使用IBIS-AMI模型估算BER仿真是唯一真正可行的方法。 去年夏季,Cadence为DDR4提供了第一款IBIS-AMI模型,并于今年初在DesignCon上进行展示。

与串行链路相比,DDR的另一个变化是:由于它是一个并行接口,因而存在码间干扰和同步开关噪声,这些都需要在总线特性仿真中捕获。

针对DDR5的AMI

首先请注意,JEDEC还没有最终确定DDR5标准,因而任何改变都有可能发生。但是既然已经临近发布,那么关键问题如数据速率的改变几率则非常之低。如下是相关描述:

基于掩膜的合规性检查(应用于DDR4中,前文已做讨论)将继续进行

电源电压将从DDR4的1.2V降至DDR5的1.1V

数据速率将高达6.4 Gbps

片上端接(上拉VDDQ)可用于地址总线,而不仅仅局限于数据总线

FFE、CTLE和DFE预计将在控制器端用于数据总线

数据总线方面,DFE也将应用于内存端

$ r; I; S" i5 n2 |r4 }& A

如此看来,通道仿真和AMI Builder将成为引领未来设计的关键所在,特别是对于需要首次创建AMI模型的新一代工程师而言。

-

接收器

+关注

关注

14文章

2486浏览量

72488 -

串行链路

+关注

关注

0文章

7浏览量

8204 -

DDR5

+关注

关注

1文章

433浏览量

24332

原文标题:技术干货 | 了解AMI与IBIS之后你需要知道:如何轻松完成DDR5设计

文章出处:【微信号:eda365wx,微信公众号:EDA365电子论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

未来谁主沉浮:串行和并行接口SRAM对比

串行DataFlash 存储器及其与单片机的接口

增强型并行端口EPP与FIFO存储器IDT7201的接口电路

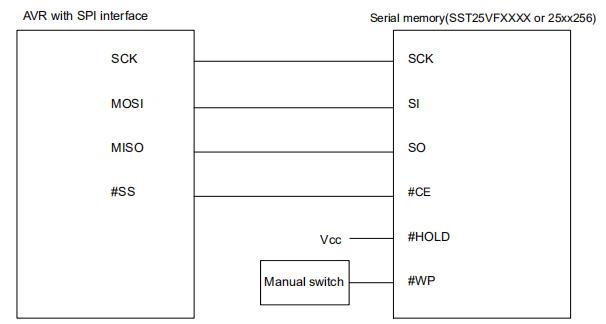

串行外设接口(SPI)扩展大容量数据存储器

SRAM存储器的并行接口和串行接口对比

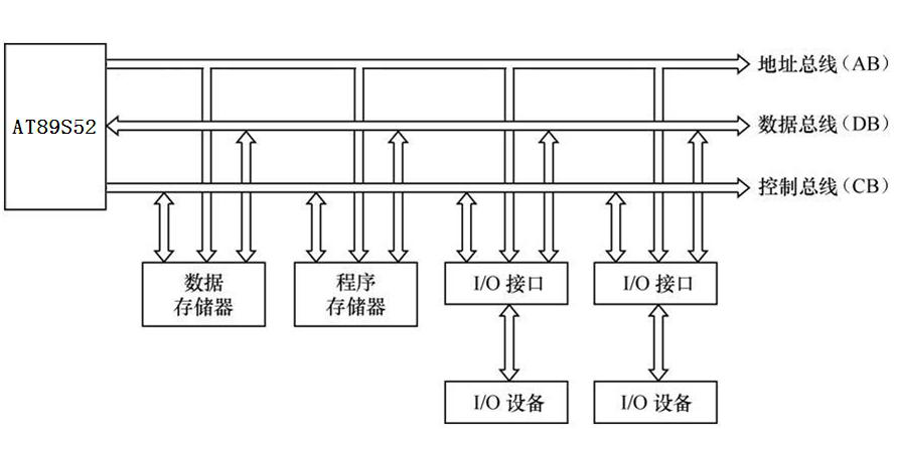

AT89S52单片机外部存储器的扩展教程课件免费下载

基于AT45DB161B存储器和PIC16LC73B单片机实现微型压力测量装置设计

分析串行链路的技术正在扩展应用到并行存储器接口领域

分析串行链路的技术正在扩展应用到并行存储器接口领域

评论