RCC时钟模块并不好理解,初次接触我也是一头雾水,而且我真正掌握它的时候也比较晚,是我在学习uC/os-II,需要分析时钟时才有了深刻认识。但在学习中我却一定要把放在了前列,因为这是整个嵌入式最重要的基础之一,可以说是M3芯片的心脏。初学者理解是比较困难,但是掌握清晰对于嵌入式操作系统特别是Timer定时器以及通讯领域具有重大意义。

下面进入正题,先上一张RCC模块的结构图:

初看此图是不是感觉太复杂了,事实上我第一次看这张图的时候也是的,完全理不清结构,不过不用担心,下面我就分层带你来理解这幅图。

(1)时钟源(4个晶振源,1个中介源)

HSI(RC):内部高速晶振,~8MHz

HSE(Osc):外部高速晶振(与电路设计时选择有关,25MHz)

LSE(Osc):外部低速晶振(默认为32.768KHZ)

LSI(RC):内部低速晶振,~40KHz

PLLCLK:锁向环倍频输出,最大频率小于72MHz,注:PLLCLK来源HSE,HSE/2,HSI/2

(2)系统时钟源

SYSCLK:系统时钟

来源HSI,PLLCLK,HSE,若CSS(时钟监视系统)检测到HSE失效,SYSCLK = HSI;

(3)主要输出时钟源

HCLK:高性能总线时钟(SYSCLK通过AHB Prescaler,最高72MHZ)

PCLK1:外设1区域时钟(通过APB1 Prescaler,最高36MHZ)

PCLK2:外设2区域时钟(通过APB2 Prescaler,最高72MHZ)

此外APB1,APB2外设时钟除了给对应外设区域提供时钟外,还可通过TIMERX Prescaler分配不同的定时器时钟。

ADCCLK:ADC外设时钟(PCLK2通过ADC Prescaler)

USBCLK:通用串行接口时钟(PLLCLK通过USB Prescaler,等于48MHZ)

RTCCLK:实时时钟,来源LSI,LSE,HSE/128

IWDGCLK:独立看门狗时钟,来源LSI

MCO:输出内部时钟

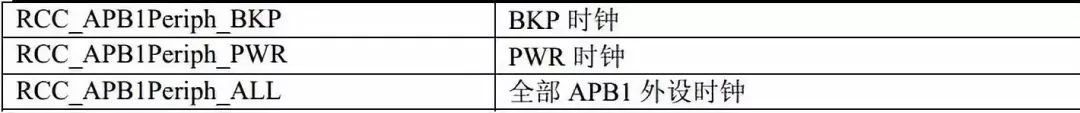

从上面看,我们前面学到的GPIOD外设还有后面的USART等的时钟都没有提到,为什么,其实它们包含在PCLK1,PCLK2这两个外设区域时钟里,也就是说他们的外设时钟来源于该区域的时钟。下面是STM32Fxxx固件函数库中15.2.22以及15.2.23所提到的图,包含所有外设对应的区域:

PCLK1时钟区域:

PCLK2时钟区域:

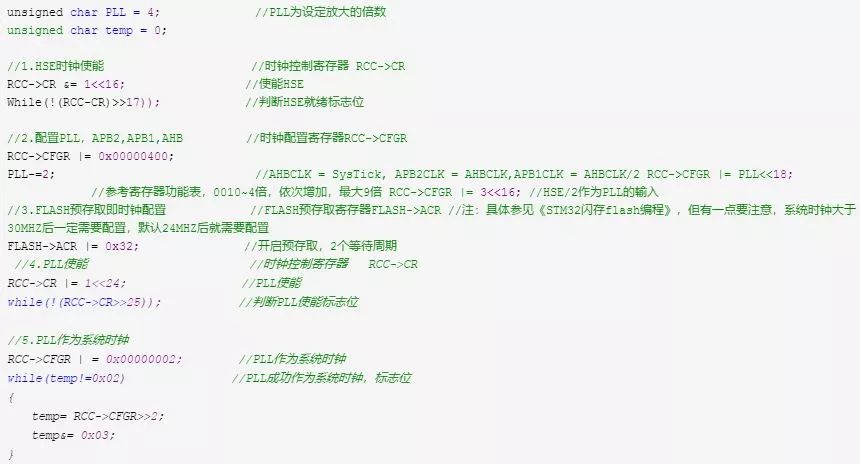

了解了这些其实已经对系统时钟掌握差不多了,下面我就以寄存器控制方式展现嵌入式时钟的配置(库函数操作对于理解时钟配置过程的帮助并不大,特别只是单纯调用而没有理解每个函数内容的情况下)。

(4)系统时钟配置实例(以使用HSE晶振,最后系统时钟为50MHZ为例)

注:RCC寄存器功能可参考《STM32中文参考手册》6.3(互联型产品)

通过上述方式就完成了时钟的一般外设的时钟初始化设置,配置系统时钟50MHZ,APB2外设时钟50MHZ,APB1外设时钟25MHZ,理解了这些,延时时间和通讯速率等通过计算即可精确的知晓,这对于整个stm32的学习以及后续理解嵌入式实时操作系统都具有重要意义。

-

RCC

+关注

关注

0文章

93浏览量

26892 -

时钟模块

+关注

关注

1文章

50浏览量

14361 -

时钟源

+关注

关注

0文章

93浏览量

15929

原文标题:STM32学习笔记——RCC外设的学习和理解

文章出处:【微信号:mcugeek,微信公众号:MCU开发加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DVI接口详细分析

详细分析stm32f10x.h

详细分析了VTIM和VMIN的功能

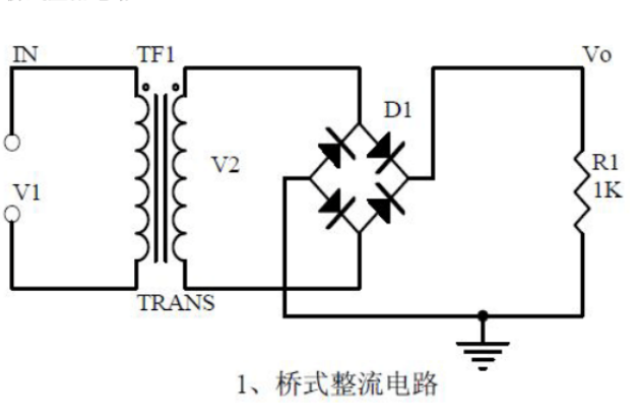

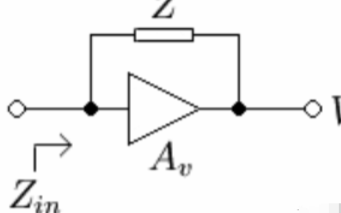

硬件工程师必须掌握的20个重要模拟电路的概述和参考答案以及详细分析

RCC时钟模块外设的详细分析和理解的资料概述

RCC时钟模块外设的详细分析和理解的资料概述

评论