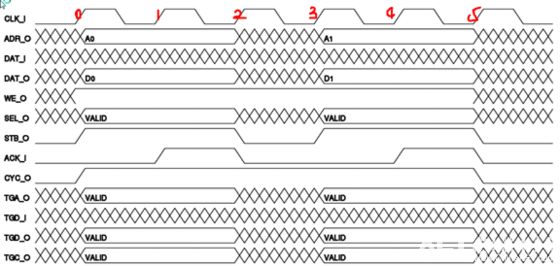

图17显示的是一个标准的块写周期时序图。块写周期可以在每一个时钟周期完成一次数据传输。但是,本例中显示了主机和从机插入等待状态以控制数据传输速率的情况。图中一共显示了5个传输。第二次传输后,主机插入了一个等待状态。第四次传输后,从机插入了一个等待状态。整个周期在第五次传输之后结束。

图17 标准块写周期

总线协议的执行流程如下:

时钟上升沿0:

·主机将有效地址置于ADR_O()和TGA_O();

·主机将WE_O置位,以表明进入写周期;

·主机输出SEL_O()(bank select)表明其操作的数据地址;

·主机将CYC_O和TGC_O()置位,以表明周期的开始;

·主机将STB_O置位,以表明第一个段(phase)的开始;

注意:主机可以在时钟上升沿1之前的任意时间,将CYC_O和TGC_O()置位。

时钟上升沿1:

·从机解码输入,并作出从机响应(ACK_I)。

时钟上升沿2:

·主机将监控ACK_I信号;

·主机将STB_O复位,以插入一个等待状态(-WSW-)。

时钟上升沿3:

·主机将有效地址置于ADR_O()和TGA_O();

·主机将WE_O置位,以表明进入写周期;

·主机输出SEL_O()(bank select)表明其操作的数据地址;

·主机将CYC_O和TGC_O()置位,以表明周期的开始;

·主机将STB_O置位,以表明第二个段(phase)的开始。

时钟上升沿4:

·主机将有效地址置于ADR_O()和TGA_O()

·主机将WE_O复位,以表明进入读周期;

·主机输出SEL_O()(bank select)表明其操作的数据地址;

·主机将STB_O置位。

·从机解码输入,并对ACK_I做出相应。

时钟上升沿5:

·主机监控ACK_I信号;

·主机将STB_O和CYC_O复位,以结束本次块读周期。

流水线块写操作

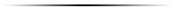

流水线块写模式的时序图如图18所示。

图18 流水线块写周期

总线协议的执行流程如下:

时钟上升沿0:

·主机将有效地址置于ADR_O()和TGA_O();

·主机将WE_O置位,以表明进入写周期;

·主机输出SEL_O()(bank select)表明其操作的数据地址;

·主机将CYC_O和TGC_O()置位,以表明周期的开始;

·主机将STB_O置位,以表明第一个段(phase)的开始;

·主机监控ACK_I信号,并准备锁存DAT_I()和TGD_I()信号。

时钟上升沿1:

·从机解码输入,并作出从机响应(ACK_I);

·主机将有效地址置于ADR_O()和TGA_O();

·主机将WE_O置位,以表明进入写周期;

·主机输出SEL_O()(bank select)表明其操作的数据地址;

·主机将STB_O置位,以表明第二个段(phase)的开始。

时钟上升沿2:

时钟上升沿3:

·从机解码输入,并作出从机响应(ACK_I);

·当STALL_I为低电平时(inactive),主机将STB_O信号复位。

时钟上升沿4:

·主机将CYC_O信号复位,当接受到第二个ACK_O信号时。

-

数据传输

+关注

关注

9文章

1880浏览量

64553 -

主机

+关注

关注

0文章

993浏览量

35114

原文标题:【博文连载】Wishbone总线周期之块写操作

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

怎么由芯片的时序图写它的程序?

请问如何用proteus仿真出8086的总线周期时序图?

求助:有哪位大神用过AD977,怎么用Verilog写它的时序图

关于单片机时序图分析

【转帖】教你看懂时序图

教程 | SDRAM读写时序介绍(配时序图)

怎么由芯片的时序图写程序?_单片机对1602液晶时序图编程设计

关于块写周期时序图的应用

关于块写周期时序图的应用

评论