本文介绍了在企业产品研发时一些经常出现的 EMC 问题,并提出了相应的解决策略。

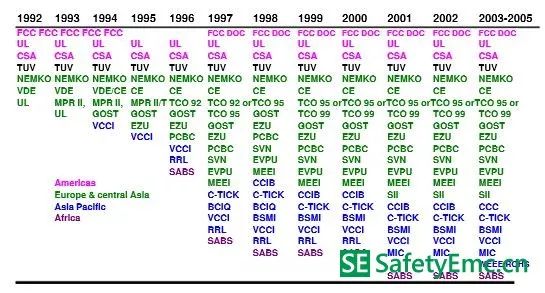

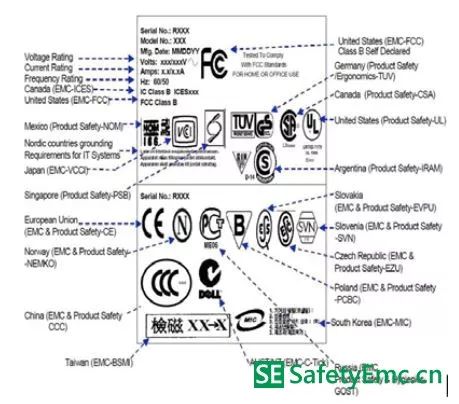

目前世界各个国家的产品认证法规要求任何电子相关 产品在本国销售必须带有相应标识,以表明产品符合安全和 电磁兼容的标准要求。如中国的 CCC 认证,美国的 FCC 和欧盟的 CE 认证等, 已成为 WTO 规则中的技术贸易壁垒 (TBT ) , 如图 1和图 2所示。

EMC 的指标是目前在所有法律法规所要求的项目中,在产品设计时最难以达到的。 2006年调查表明,EMC问题是 电子工程师在研发设计是遇到的最大挑战,由于EMC的设计 经验较少,经常在设计完成之后才进行 EMC 的测试,一旦测 试发现问题,会出现产品准备上市销售了,EMC 的问题总是 没有时间来解决,项目总是要不断的延迟,需要再花费大量 的时间去解决,相信这是每位遇到 EMC 问题的研发人员的深刻体会。

所以解决 EMC 的问题应该在产品研发的过程之中予以 解决,而不是在产品研发完成之后再进行修补,在设计中应 遵循一些 EMC 的设计导则,项目团队对电路设计和 PCB 设计 进行评审,并在每个研发阶段应进行相应的 EMC工程测试,以发现潜在的问题。

从 EMC 问题产生的根源上解决问题永远比在表面上解 决(如屏蔽)要好的多,且成本更低,且在整个项目研发流 程中,对 EMC 问题解决的越晚,所产生的成本会更高。

由于各个 EMC 的测试项目不同,问题产生的原因也不 尽相同,相应的解决方法也不同,产品设计中常见的电磁兼 容性问题有以下几种。

一、辐射发射无法满足标准要求问题

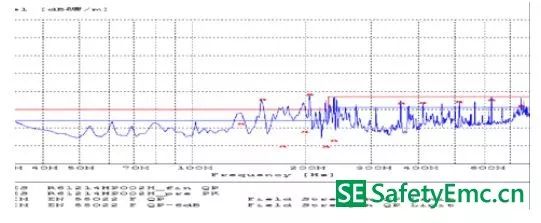

典型的产品电磁辐射问题如下图 3所示,有一些频率点 上超出标准的要求,由于辐射发射的测试不确定度很大,各 个实验室之间的测试结果差异很大,许多公司都要求辐射发 射的测试结果有 4-6dB 的裕量。

类似辐射发射超标的情况经常发生,要想解决,须弄清 楚辐射产生的根本原因,据笔者分析,可能的辐射问题来源 有 [1]:

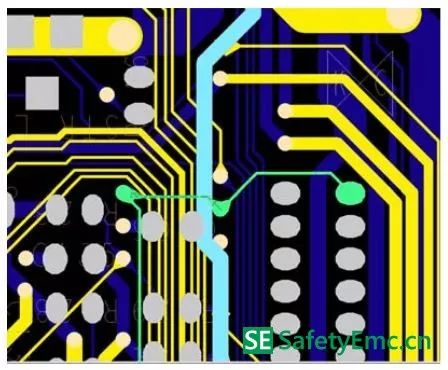

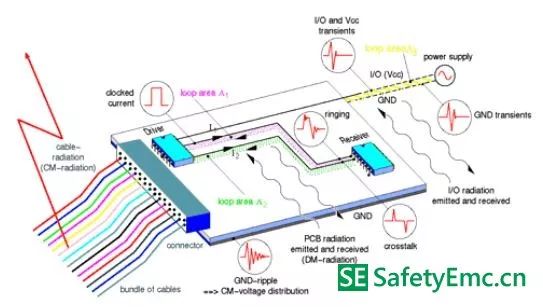

1.印刷线路板中走线问题引起的 ,如图4.

在 PCB 板走线中应该注意一些高速信号的回流路径,我们知道信号即有电压也会存在电流,而信号电流总是要流 回其源头,如果高速信号的回流路径过大,形成环路,很容 易对外辐射能量。

2.连接 PCB 板的电缆引走的问题,如图 5。

而与电路板相连的电缆也是产生辐射问题的原因之一, 因为高速信号电流在电缆中流动由于环路和阻抗不匹配等 原因很易对外产生共模或差模的电磁辐射。

3. 电路中某些器件的快速切换。

高速电路中存在着众多的高速器件,高速器件在快速的 切换时会产生大量的电流的高速变化,从而引起能量的辐 射。

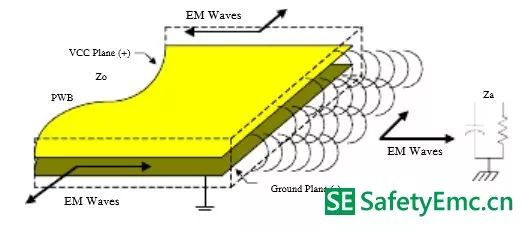

4. 多层印制板的板层设计不合理

图 6 PCB板间的电磁场分布

在多层电路板中,如果叠层设计不合理,叠层之间的电 磁场耦合存在天线效应,对外进行能量辐射,如图 6所示。

图 7 信号走线问题仿真分析 [3]

辐射的能量从哪里出来,如何解决?通常要花费工程 师相当长的时间来进行分析解决。图 7的仿真分析结果则很 清晰表明的产生辐射问题的机理,在高频状态下,电流总是 寻找最短路径回到源端,在存在障碍的情况下(高阻抗、环 流面积大)就会对产生辐射。

屏蔽是解决辐射问题的直接办法,但却不能根除问题 根源,并会带来许多其他问题,设计成本会上升,且在产品 生产中增加工艺的复杂性,生产成本也会增加。所以说屏蔽 是解决辐射问题的最后的办法, 绝大多数的问题都可以用最 简单的办法,也是最低成本的办法于以解决。

分析信号特性,找出问题根源,进行信号设计和 PCB 板的良好设计是解决此类问题的最佳方案, 几乎不用增加任 何成本。

二、 ESD 静电放电测试无法通过

静题的测试项目之一, 经常发生的失效现象有系统死机,系统复位,显示面板出现错误, 发生上述问题的根本原因是静电放电电流耦合到电路板中的某些走线上进入 CPU 内部, CPU 在信号状态突变时 无法有效处理或干扰引起的运行中断导致无法回复到原来 的状态,静电放电测试也是一项破坏性的测试项目,产生的 静电放电电流会经常导致器件发生物理性损坏, 这一点需要在测试中注意。

基于以上分析,在电路设计中应对于可能进行 ESD 测 试的部件进行一些处理(包括系统良好接地,控制面板绝缘 处理,关键信号隔离滤波,通信协议的容错分析,专用接地 层的使用等)。

尽管在设计时进行了大量的考虑,采取一些防止 EMC 问题的方法,但在实际测试中还会可以出现问题,这就是 EMC 问题的特性,无法预测, 在发生 ESD 问题时,解决方案有:

- 改进系统的接地设计(包括机箱机柜、控制面板、通 信电缆连接)。

- 改进电路板的接地设计,对外接口 ESD 接地的设计。

- 发现系统死机、复位或通信错误的根本原因,在 PCB 板进行相应信号处理和在软件上进行处理, 也解决 ESD 问题 的最好办法,费用最低,但难度较大、较为耗时。

三、 产品的辐射抗扰度问题

产品的辐射抗扰度测试是在全电波暗室中进行如图 9

所示,标准的测试场强等级有 1V/m, 3V/m和 10V/m, 汽车类 电子产品的测试方法有所不同。

数字电路相对于模拟电路的抗辐射干扰能力要强的 多,在辐射抗扰度测试过程中,多数出现问题的是带模拟电 路的产品, 测试中常出现的问题有在某些频率上产品的信号 输出变化巨大(如图 10所示) ,通信出现错误,或系统复机 死机。

所示,标准的测试场强等级有 1V/m, 3V/m和 10V/m, 汽车类 电子产品的测试方法有所不同。

数字电路相对于模拟电路的抗辐射干扰能力要强的 多,在辐射抗扰度测试过程中,多数出现问题的是带模拟电 路的产品, 测试中常出现的问题有在某些频率上产品的信号 输出变化巨大(如图 10所示) ,通信出现错误,或系统复机 死机。

此类问题主要出现于通信类产品和带有信号采信、用模拟 电路进行信号处理的产品中, 其根源与其他的 EMC 抗扰度问题类 似, 是干扰进入 CPU 内部影响其正常运行, 对于模拟电路的产品, 信号在进入模数转换之前的信号滤波很重要。

一旦出现测试通不过的问题,判断出到底根源在哪里是很 不容易,解决难度相当的大,且相当耗费时间和精力,在实验室 中测试成本大幅上升。

解决方案有包括:- 系统的良好的接地设计(包括机箱机柜、控制面板、通信 电缆连接)以及完善的电路信号处理。

- 在解决产品辐射抗扰度的过程中,有一些独特办法,迅速 定位出抗扰度问题的根源, 在电路设计上采用相应的措施用以解 决此类问题,不建议采用屏蔽的办法来解决。

四 其他传导类的电磁干扰如电快速瞬变脉冲群抗扰 度、浪涌和射频传导抗扰度测试也会发生问题,但解决 起来会比较容易一些,在此不再垒述。

结束语

以上是在为企业产品研发进行电磁兼容咨询和解决问题的 过程中的一些体会,写出来与大家其享,希望大家在进行产品设 计的过程中不要因为 EMC 的问题造成麻烦,也希望利用自己的 一些经验帮助大家避免和解决产品研发中的 EMC 问题,也借此 机会与大家交流,文中有不妥的地方,请批评指正,谢谢!

-

电子产品

+关注

关注

6文章

1183浏览量

58743 -

emc

+关注

关注

170文章

3986浏览量

184350 -

辐射发射

+关注

关注

0文章

42浏览量

11795

原文标题:20180716-产品设计中的常见电磁兼容问题及解决策略

文章出处:【微信号:EMC_EMI,微信公众号:电磁兼容EMC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电子产品结构与导热材料解决方案

[原创电子产品逆向设计的相关资料〈抄板软件+PCB返原理图〉

项目管理在电子产品研发中的应用

EMI/EMC 设计秘籍 ——电子产品设计工程师必备手册

电子产品认证检测中的EMC问题及其分析(77页PPT)

卷发棒单片机芯片方案—专注电子产品方案开发

电子产品的检修方法

【活动】如何做电子产品EMC设计评估?参与免费送课!

车载电子产品各种需要EMC测试的项目和设计要点的详细概述

电子产品产品研发时经常出现的EMC问题,有什么解决方案?

电子产品产品研发时经常出现的EMC问题,有什么解决方案?

评论