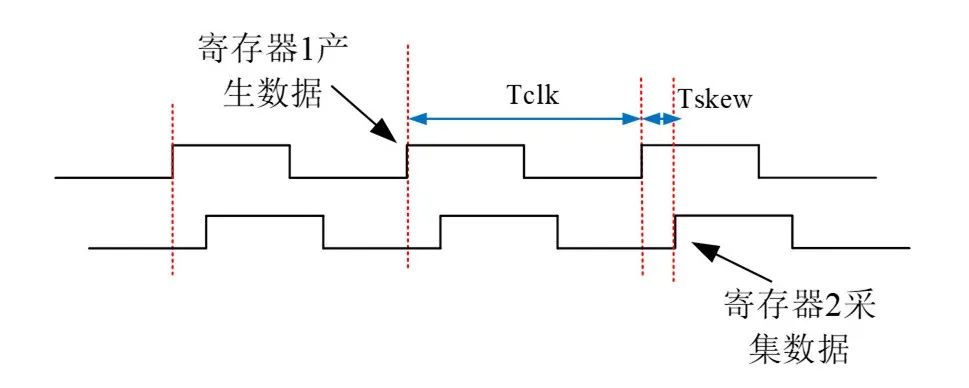

今天要介绍的时序分析基本概念是skew,我们称为偏差。由于时钟到每个寄存器的路径延迟不一样,造成信号到达clock pin的时间也不一样,我们把时钟信号到达不同寄存器的时间偏差称为skew。一直以来,Skew都是衡量时钟树性能的重要参数,传统CTS的目的就是为了减小skew。

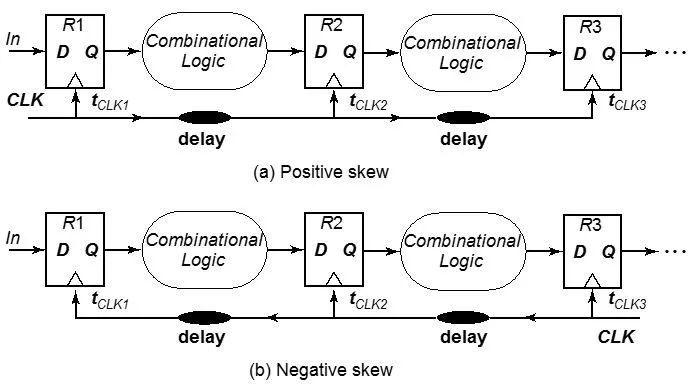

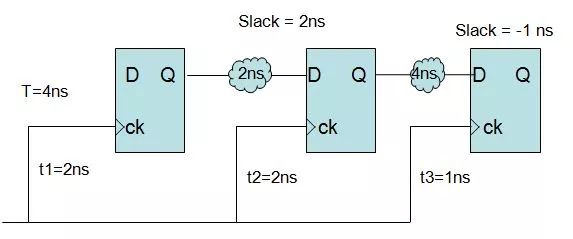

Skew的类型分为很多种,根据clock和data path的方向,skew可以分为positive skew和negative skew。如下图所示:

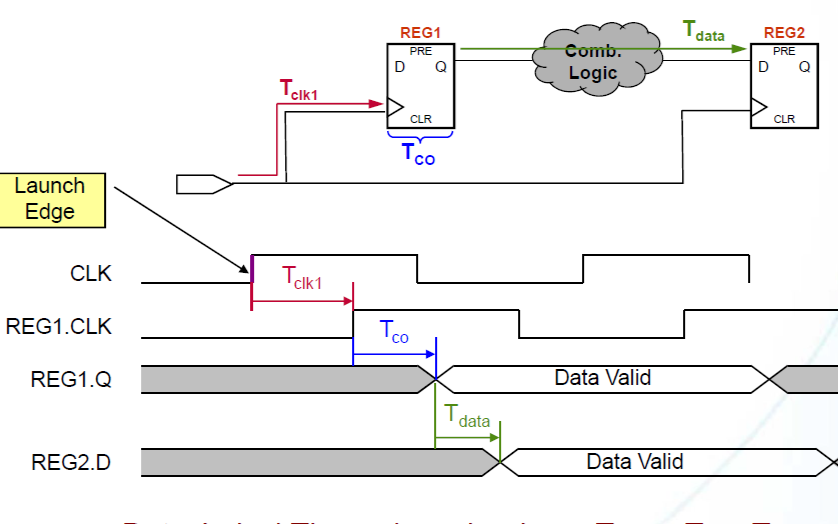

对于positive skew,clock和data path在相同方向上。反之对negative skew来说,clock和data path在相反方向上。那它们对我们的design有什么影响呢?我们来看一下setup和hold的计算公式:

我们可以得到以下结果,

对于positive skew来说,它可以减少T的时间,相当于提升芯片的performace。但是它的hold时间会变得更加难以满足

对于negative skew来说,它的hold时间更加容易满足,取而代之的是,它会降低芯片的性能。

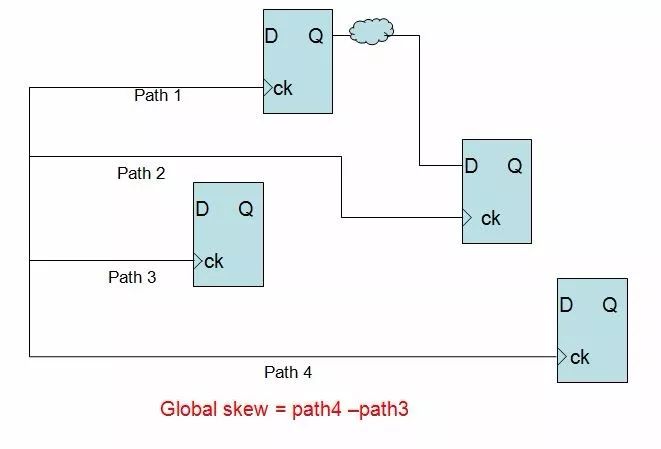

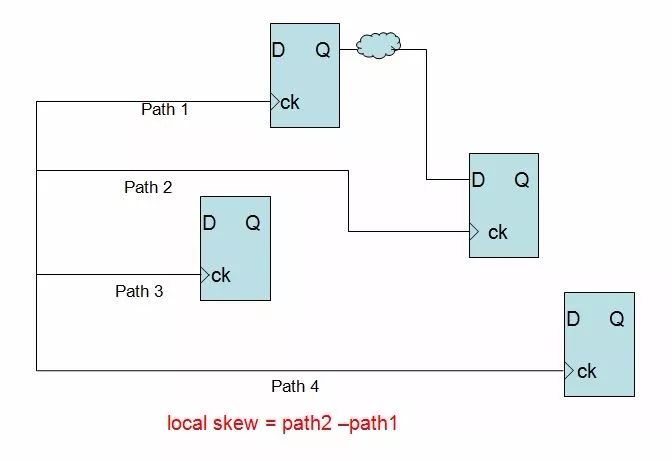

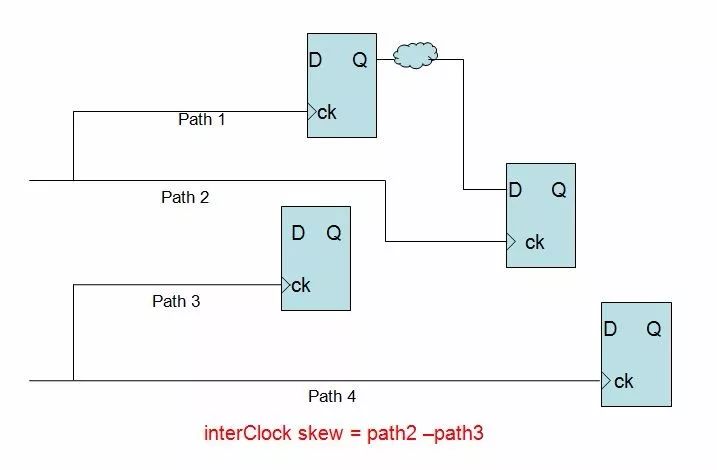

还有另外一种skew的分类方法,是我们更为常见的,根据时钟域以及路径关系,skew可以分为global skew,local skew,interclock skew。

Global skew是指,同一时钟域,任意两个路径的最大skew 。如下图所示,注意是任意两条路径,不管是不是timing path,都会算作gloabl skew计算的对象。CTS时,工具更关注的是global skew, 会尽可能地将global skew做小。

Local skew是指,同一时钟域,任意两个有逻辑关联关系的路径最大skew 。这边需要注明,必须是存在逻辑关系的path才会计算local skew,也就是说必须要是timing path。如下图所示,我们在分析timing的时候,更多地是关注local skew。

interClock skew是指,不同时钟域之间路径的最大skew,如下图所示:

另外还有一种比较特使的skew,就是现如今用得较多的useful skew,我们称为有用偏差。一般来说,skew会恶化timing结果,但如果合理使用,那skew也可以起到修复timing的作用,从而提高设计的频率。

如下图:时钟周期为4ns,各时钟路径延迟如下:可以看到有一条路径的slack为-1ns,说明这条路径违规。可以看到与这条路径相关的skew是t3-t2= -1ns。

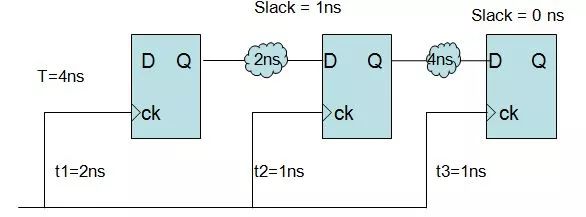

下面我们利用useful skew向前面一个slack比较充裕的路径(slack=2ns)借用1ns的时间,这样两条path都meet了时序要求。如下图:

这就是useful skew的作用,可以向前,或者向后借time来修正violation。

-

寄存器

+关注

关注

31文章

5619浏览量

130393 -

时序分析

+关注

关注

2文章

130浏览量

24273 -

时钟信号

+关注

关注

4文章

509浏览量

30078

原文标题:时序分析基本概念介绍

文章出处:【微信号:IC_Physical_Design,微信公众号:数字后端IC芯片设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

基于FPGA的时序分析设计方案

时序分析之useful skew的作用分析

时序分析之useful skew的作用分析

评论