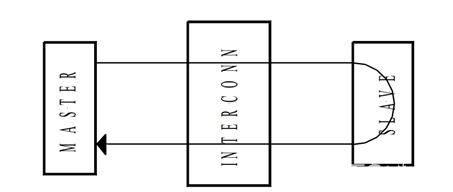

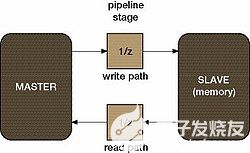

为了实现在给定时钟频率下的最大可能吞吐量,Wishbone采用了周期异步结束方式。这样做的结果是从主设备的STB_O到从设备的ACK_O/ERR_O/RTY_O再到主设备的ACK_I/ERR_I/RTY_I输入形成了一个异步回路,如图23。在大型SoC设计中,该回路往往成为整个设计的关键路径,限制系统时钟频率的进一步提高。在深亚微米时代,由于线延迟往往比门延迟更大,这一异步回路更加可能成为系统性能的瓶颈。

图23 Wishbone总线的异步周期结束路径

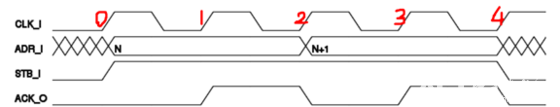

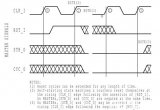

这一问题的最简单解决方法是插入寄存器将回路断开,但这样做的缺点是在每一次总线操作中都需要插入一个等待周期,从而制约了总线吞吐量。如图24所示,在上升沿0主设备发起了一次操作,在上升沿1从设备发起响应将ACK_O置高,在上升沿2主设备检测到ACK_I为高完成第一次操作并发起第二次操作,但是在上升沿2从设备并不知道主设备会发起第二次操作,因此只能将ACK_O信号置低。在上升沿3从设备才能对第二次操作发起响应将ACK_O置高,在上升沿3主设备检测到ACK_I为高完成第二次操作。

图24 Wishbone总线的传统同步周期结束方式

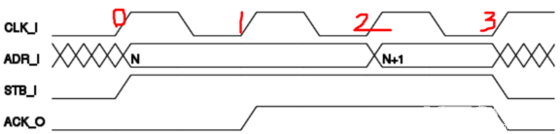

在图24中,每一次传输都需要两个时钟周期,一半的带宽被浪费。如果从设备在上升沿3知道主设备将发起新的操作,它将能够在上升沿3就对主设备的操作发起响应,从而节省时钟周期提高了系统的吞吐量,利用该思想改进后的同步时序如图25所示。

图25 Wishbone总线改进的同步周期结束方式

在图25的上升沿1,主设备发起操作,在上升沿2,从设备将ACK_O置高,在上升沿3,从设备知道主设备将发起新的操作,于是将ACK_O继续置高。因此, 3个时钟周期就完成了2次操作,而不是原来大的4个时钟周期,于是吞吐量提高了25%。一般的,改进后,N次操作需要N+1个时钟周期,而不是2N个时钟周期,吞吐量改善为(N-1)/N%。

改进后的同步周期结束方式具备异步周期结束方式的吞吐量优势,同时具备传统同步结束方式的延迟优势。改进后的同步周期结束方式称作Wishbone寄存反馈周期结束方式。

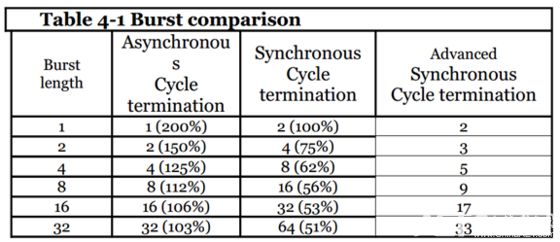

表2 优化结果比较

-

寄存器

+关注

关注

31文章

5377浏览量

121396 -

总线

+关注

关注

10文章

2908浏览量

88489 -

Wishbone

+关注

关注

0文章

16浏览量

10448

原文标题:【博文连载】Wishbone总线同步结束与异步结束对比

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

wishbone总线

基于WISHBONE总线的FLASH闪存接口设计

基于Wishbone片上总线的IP核的互联

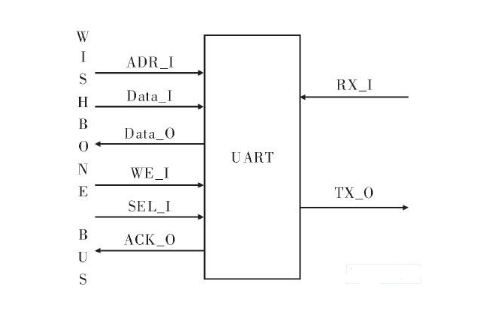

基于Wishbone总线的UART IP核设计

基于WISHBONE总线的FLASH闪存接口设计

基于WISHBONE总线的通用接口控制器

Wishbone总线实现UART IP核设计

基于FPGA的SDX总线与Wishbone总线接口设计

Wishbone一般总线规范的共同特点

Wishbone总线的突发结束

Wishbone总线的主要特征概括

Wishbone II交易总线:速度的另一个等级

Wishbone总线的异步周期结束路径

Wishbone总线的异步周期结束路径

评论