高速PCB板中,走线不仅仅是连接两个点。作为一名合格的工程师,走线就是包括电阻,电容,电感的混合知识载体。信号线在传输过程中会有反射现象,这个必须要了解一下,负载端反射的大小取决传输线的Z和负载的Z。

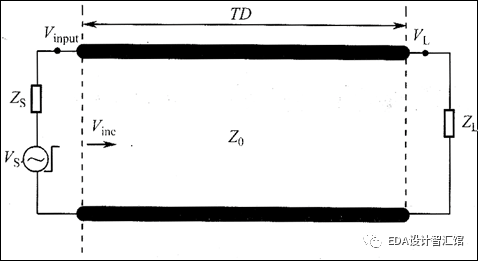

系统模型如下图:

信号被反射的大小用反射系数KR来衡量,负载端的反射系数为:KRL=(ZL—Z0)/(ZL+Z0),对于开路负载,KRL=1;对于短路负载,KRL=-1可见,对于开路和短路负载,信号被100%反射回来了。KRL为负值表明被反射的信号与原信号方向相反。同样,信号在源端反射的大小用源端的反射系数表示:KRS=(ZS—Z0)/(ZS+Z0)。

设驱动器的标准输出电平为0.2V,电流 24mA,则其输出阻抗ZS约为8.3Ω。设负载的输入阻抗ZL大于100KΩ,远大于Z0(约为67Ω),则负载端反射系数为:KRL=1,信号在负载端被100%反射。源端反射系数为KRS=-0.78。

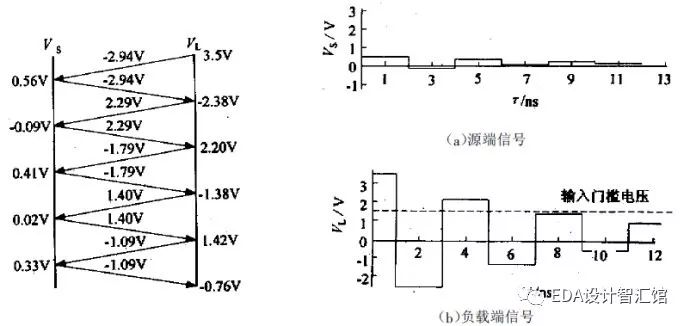

下面来具体分析驱动器产生一个从3.5V切换至0.2V信号的反射过程。

第1次反射:驱动器电压为3.3V,根据ZS与Z0组成的分压原理,Z0上产生的信号△V=-2.94V,源端信号电压为VS=O.56V。负载端反射系数为1。当信号到达负载端时,VL=3.5-2.94-2.94=-2.38V。

第2次反射:开始源端信号为0.56V,当-2.94V信号到达源端发生第二次反射,反射电压为:VR=KPS*△V=-0.78*(-2.94)=2.29V。所以源端电压变为VS=0.56+(-2.94)+2.29=-0.09V。

第3次反射:当第2次反射信号到达负载端时,负载端电压变为:

VL=-2.38+2.29+2.29=2.2.V

在这种阻抗不匹配的传输线上,信号就是这样来回反射,每反射一次其幅值就减小一些,直至最后消失。此过程如图2所示,左侧和右侧的竖线分别代表源端和负载端的电压,斜线则标明了传送信号和反射信号电压的大小。也可以用图3来表示信号的具体反射过程,图3(a)表示源端信号,图3(b)表示负载端信号。可以看到在经过5个周期以后传输到负载端的信号才下降至输入门槛值以下,传输延时一般介于6——16ns/m之间,若传输延时tPD=10ns/m,,则通过一根0.15m的传输线的延时约为1.5ns,那么该信号在传送出去大约13.5ns之后才可以认为是有效的。

-

高速设计

+关注

关注

0文章

23浏览量

11432 -

信号反射

+关注

关注

0文章

16浏览量

10480

原文标题:信号反射怎么搞?高速设计中要这样来

文章出处:【微信号:PCBTech,微信公众号:EDA设计智汇馆】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高速PCB设计中的反射研究

高速信号的反射是如何形成的?资料下载

一文了解高速设计中的信号反射

一文了解高速设计中的信号反射

评论