阐述了S波段小型化发射通道电路原理,并对设计方案与测试结果进行分析。软件仿真腔体谐振,通过合理设计腔体结构能够保证腔体谐振点远离所用频率范围。在设计中采用MEMS滤波器、微波单片集成电路芯片及微组装薄膜工艺来实现通道小型化。测试结果表明,该S波段小型化发射通道增益平坦度小于1 dB,带内杂波抑制大于80 dBc,本振抑制大于57 dBc,三阶交调抑制大于66 dBc。整个发射通道尺寸为55 mm×35 mm×14 mm,其性能优异且集成度高。

0 引言

上变频模块在雷达、通信等方面有着十分重要的作用,一般把低频段信号上变频变换到符合发射机所要求的频段范围内,再通过发射天线将信号发射出去。要实现电路整体设计的小型化[1],需要从复杂、繁琐的级联电路设计中解脱出来。本文利用MEMS滤波器、微波单片集成电路(MMIC)芯片、频率源及微组装薄膜工艺来实现通道小型化,最后对该发射通道进行测试,性能满足指标要求。

1 电路设计

1.1 电路原理及主要技术指标

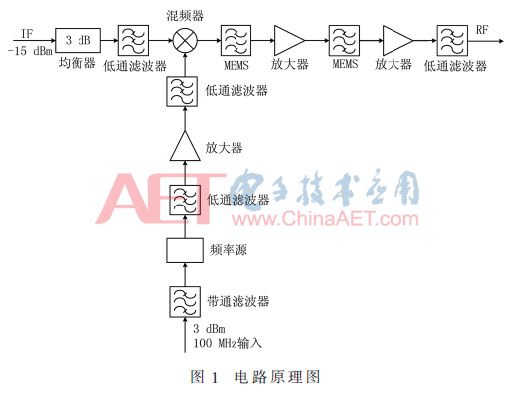

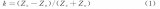

正面射频一路主要由均衡器、中频低通滤波器、混频器、两级MEMS滤波器、两级放大器及射频低通滤波器电路组成。

背面本振一路主要由带通滤波器、放大器、低通滤波器、频率源构成。加入带通滤波器主要出于EMC电磁兼容考虑,加入低通滤波器是为了滤掉频率源谐波。电路原理如图1所示。

指标要求具体如下:

(1)中频输入频率:0.47 GHz~0.97 GHz;

(2)中频输入功率:-15 dBm;

(3)射频输出频率:3.8 GHz~4.3 GHz;

(4)参考输入频率:100 MHz;功率:3 dBm;

(5)本振频率:3.33 GHz;

(6)增益:10±1 dB;

(7)增益稳定度:≤2 dB;

(8)增益平坦度:≤1 dB;

(9)带内杂波抑制:≥60 dBc;

(10)本振抑制:≥55 dBc;

(11)三阶交调抑制:≥55 dBc;

(12)谐波抑制:≥55 dBc;

(13)输入、输出驻波:≤1.5;

(14)工作电压:+5 V。

1.2 盒体结构设计

为满足本振抑制指标,要求本振信号与射频信号分腔处理,使用金属隔墙完成本振信号与射频信号的隔离,使得本振信号在射频输出端口抑制更高,同时合理设计腔体结构,充分利用有效空间,减小模块尺寸,实现小型化设计。

腔体分为上下两部分,下层腔体放置本振频率源电路,上层腔体布置薄膜基板射频电路。本振频率源电路使用多层环氧板制作,独立完成贴装元器件后,通过螺钉将其拧固到盒体上。上层腔体布置射频电路,元器件通过导电胶粘接到盒体,保证良好的接地性能,上、下层通过绝缘子互连。腔体结构示意图如图2所示。

为了避免外界环境对器件性能的影响,一般设计腔体来保护器件[2]。在射频电路中,一个封闭的腔体管壳相当于谐振腔。因此在设计腔体时,要避免腔体在放大器的工作频率范围内产生谐振导致放大器自激。如果一个腔体内放大器的总增益超过40 dB,很容易引起放大器自激。若腔体的长、宽、高分别为l、a、b并满足l>a>b时,可以得到谐振条件为:

给定腔体下的谐振频率不止一个,而有无限多个。设计腔体管壳大小要使谐振腔的谐振频率远离器件的工作频率。本方案中上层腔体通过软件仿真计算谐振频率为18.2 GHz左右,见图3。本文中选择的放大器在该频率点的总增益已经远远小于40 dB,所以这个发射通道输出端口不会出现因为谐振原因而引起自激。

1.3 主要指标技术分析

1.3.1 带内杂波指标设计

杂波是混频器变频的一个重要指标,因此一次变频混频器采用双平衡混频器,同其他混频器相比具有工作频带宽、组合干扰[4]少、动态范围大、噪声小、本振与射频、中频间隔离度高等优点,再通过后端级联滤波器能够很好地实现上述高杂波抑制度的要求。模块带内抑制指标要求≥60 dBc。通过软件计算得知,会有mIF±nLO杂波频率落入带内。本文通过所选混频器杂散指标要求,见表1。

1.3.2 谐波抑制指标设计

包含有源器件高频电路的非线性系统输出信号经泰勒级数展开后可以表示为:

则输出信号的非线性部分为:

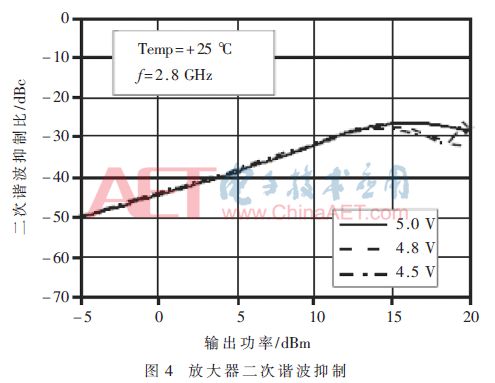

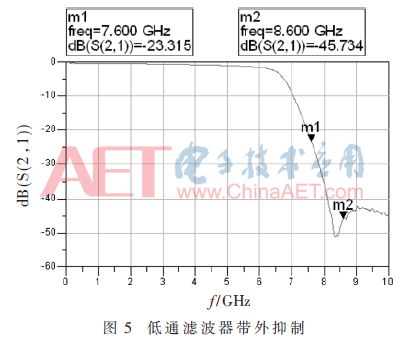

对于放大器来说,谐波频率考虑二次谐波即可。对于本方案设计,末级放大器工作频率段为0.7 GHz~5 GHz,尺寸为1.43 mm×1.15 mm×0.8 mm,P-1输出压缩点为19 dBm。实测当输出信号功率为-5 dBm时,二次谐波抑制为50 dBc。通过图4可以看出,输出压缩点一定时,基波信号输出功率越小,二次谐波抑制越高。由于末级加低通滤波器,对二次谐波7.6 GHz~8.6 GHz抑制能够达到20 dBc,如图5所示,能够保证整个频带内,二次谐波抑制都能够做到70 dBc以上。

2 微组装设计

2.1 MMIC芯片微组装

上层腔利用微组装薄膜工艺[6],减小电路布局面积和提高微组装效率,将芯片用导电胶粘接到薄膜基片上,输入输出用金丝键合将芯片互连[7-8]。芯片输入输出连接方式中,一般都会采用两根金丝键合到50 Ω微带线上进行互连。为了减小电路布局面积,提高安装效率,芯片与下一级芯片直接靠近键合连接。因芯片焊盘一般只有100 μm×100 μm,所以只采用一根键合丝连接。经过采用仿真软件进行仿真和测试,一般低于8 GHz以下,键合金丝条数一般为一根或两根即可,见图6。

2.2 MEMS滤波器应用

为实现通道小型化,滤波器采用MEMS硅腔滤波器。MEMS硅腔滤波器具有Q值高、体积小、易集成和可靠性高等优点。其工作频率从S波段到Ka波段,相对带宽为2%~100%,带外抑制可达60 dBc以上,带内群时延波动小。相同结构MEMS滤波器与腔体滤波器相比,MEMS体积是腔体的1/220[9]。

本文使用的MEMS硅腔滤波器插入损耗小于3 dB,1 dB带宽大于800 MHz,带外抑制大于50 dBc(fo±1.0 GHz),群时延波动小于1 ns,体积为7.0 mm×6.8 mm×0.8 mm。MEMS滤波器实物图和测试结果分别如图7和图8所示。

3 测试结果及分析

按以上方案设计,采用薄膜工艺及PCB板工艺实现的S波段发射通道模块实物如图9所示。由于射频通道元器件较多,各个器件级联后,输入、输出驻波会恶化,会导致带内平坦度恶化。采用中频端口混频器前加均衡器,保证带内平坦度达到指标要求。均衡器里采用空心电感来调试幅度均衡,调试灵活。电路中使用温补衰减器,可使增益值在高温、低温环境中变化小于2 dB。测量结果如表2所示。

4 结束语

该模块设计指标满足用户指标要求,利用MMIC和微组装技术大大减小发射通道的体积,降低雷达体积、重量,提高整机性能、质量和可靠性。随着单片集成电路技术的迅速发展,高密度、高可靠的微电子技术更能满足现代化雷达的要求。

-

电路

+关注

关注

172文章

5943浏览量

172550 -

滤波器

+关注

关注

161文章

7848浏览量

178461 -

射频信号

+关注

关注

6文章

218浏览量

20938

原文标题:【学术论文】S波段小型化发射通道设计

文章出处:【微信号:ChinaAET,微信公众号:电子技术应用ChinaAET】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于小型化微带双分支定向耦合器的设计方案

P波段腔体滤波器的小型化设计

电路中晶振注重超小型化空间的选择方案

电源的小型化轻量化设计方案

高效小型化的开关电源设计方案

新型C波段宽带小型化全向天线的性能分析

一款小型化L波段射频收发前端模块的设计过程讲解

小型化的微带双分支定向耦合器设计介绍

机载计算机电源的小型化设计

基于LTCC多层基板的X波段T/R组件小型化设计

小型化L波段射频收发前端模块的设计资料说明

S波段小型化发射通道电路原理,并对设计方案与测试结果进行分析

S波段小型化发射通道电路原理,并对设计方案与测试结果进行分析

评论