高速数据传输系统在通信系统、测试仪器等电子系统中有着广泛应用,人们对数据传输的处理速度、可靠性及实时性的要求越来越高,数据传输速度越来越快,对数据的抗干扰性的要求也越来越高。

01

USB3.0简介

USB3.0的最高理论速度达到了5Gbit/s,向需要更大电力支持的设备提供更好的支持和电力供应,它在USB2.0的基础上增加了新的电源管理功能,采用全双工数据通信,提供更快的传输速度,并且向下兼容USB2.0和USB1.1设备。USB体系主要包括三个部分:主机,设备和物理连接。主机通常是PC或者主机控制器;设备是指常用的U盘、带USB的摄像头、相机等设备;物理连接就是通常用的传输线,在USB3.0系统中,采用了对偶单纯形四线制差分信号线,因此可以支持双向并发数据流传输,这也是USB3.0相比于USB2.0设备速度提升的关键因素。

02

系统硬件设计

2.1 USB3.0高速传输模块

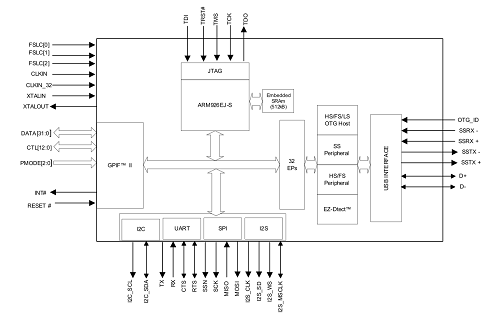

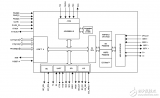

本设计采用的赛普拉斯EZ-USB FX3 CYUSB3014是新一代的USB 3.0外设控制器,其数据传输速率可达320MBps,具有高度集成的灵活特性,满足本设计的高速数据传输要求。其USB3.0模块功能框图如下图1所示。

图_1_USB3_0模块功能框图

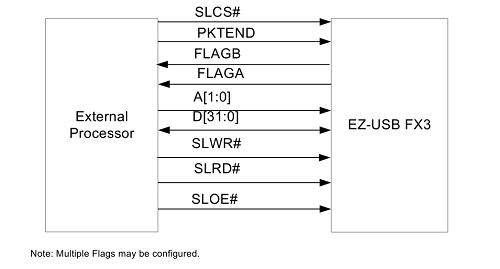

本设计中,将USB3.0模块作为从器件,从器件FIFO接口如图2所示。该接口允许外部处理器直接访问多达4个EZ-USB FX3内部缓冲区。USB3.0的控制交由FPGA,数据输出到PC机进行接收。

图_2_USB3_0从器件FIFO接口

2.2 FPGA主控模块

本设计的主控模块采用Xilinx公司的Spartan6系列FPGA,型号为XC6SLX9-2FTG256C,256个引脚的FBGA封装。开发板配置两路标准的AX扩展口,一共有34*2=68个IO口,用于外接其他模块。

将USB3.0模块的控制及数据引脚,使用杜邦线与FPGA的扩展口相连,通过对FPGA进行Verilog程序配置,来控制USB3.0的工作。实物连接如下图3所示。

图_3_FPGA+USB3.0模块实物连接图

03

系统程序设计

3.1 USB3.0模块程序设计

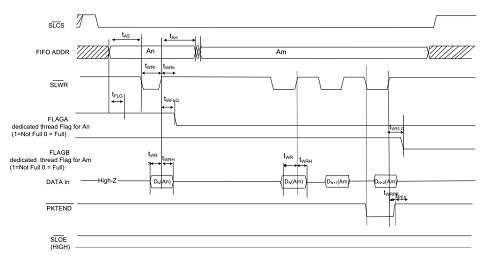

本设计以FPGA为主控模块,通过Verilog程序配置USB3.0模块的工作模式。设计中将厂商提供的固件写入到该模块,将其配置为异步、32位并行高速读写方式。在下位机采用异步从器件FIFO写入模式,其时序图如下图4所示。

图_4_异步从器件FIFO写入模式

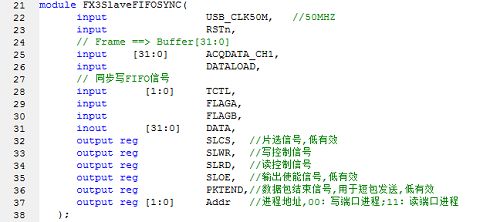

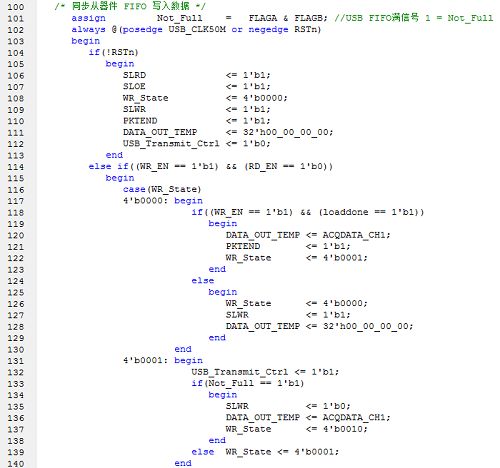

对USB3.0模块进行Verilog程序设计,其核心关键代码如下。USB3.0模块接口程序如图5所示。

图_5_USB3_0模块接口程序

USB3.0模块写入数据程序如下图6所示。

图_6_USB3_0模块写入数据程序1

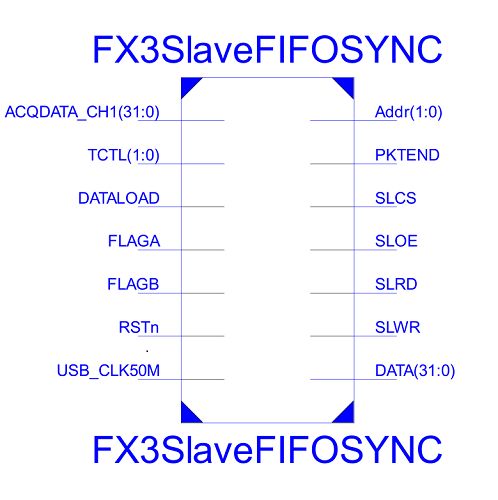

通过理解USB3.0相关手册,完成程序设计后,综合该模块,得到顶层RTL原理图,如下图7所示。

图_7_USB3_0综合顶层模块原理图

3.2 程序仿真验证

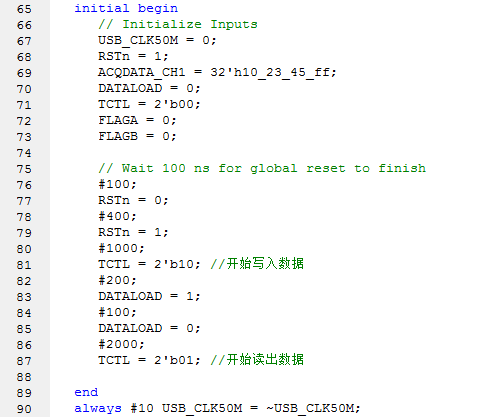

设计好上述程序后,继续编写仿真激励文件,对该模块进行仿真测试。测试核心代码如下图8所示。

图_8_USB3_0仿真测试源代码

仿真验证结果如下图9所示,可见输入数据正确控制,写入到该模块的FIFO中。

图_9_USB3_0仿真验证结果

3.3 系统实物测试

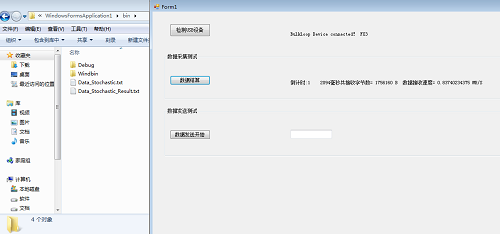

完成对程序的仿真验证后,将USB3.0的数据输出端口连接到PC机,使用接收软件进行数据接收。软件运行测试过程如下图10所示,首先与USB3.0建立连接,然后再启动数据接收。

图_10_上位机数据接收测试

04

总结

本设计的传输系统有很多优点,通过USB3.0接口的超高速传输特性,可有效地解决高速数据采集中的数据传输和存储问题,测量结果误差小,可信度高,有利于实现数据的实时处理。采用Cypress公司的USB3.0专用接口芯CYUSB3014与FPGA连接完成了采样数据的高速传输测试,经过多次测试,USB3.0接口的准确、超高速、实时等性能得到了充分的体现。

-

控制器

+关注

关注

112文章

16302浏览量

177783 -

电源管理

+关注

关注

115文章

6173浏览量

144410 -

usb

+关注

关注

60文章

7927浏览量

264404

原文标题:基于FPGA的USB3.0接口设计

文章出处:【微信号:gh_873435264fd4,微信公众号:FPGA技术联盟】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

新一代的USB 3.0外设控制器

新一代的USB 3.0外设控制器

评论